One of the quality assurance inspections that are performed in EEE parts is an external visual inspection. The applicable method for Microchip FPGAs as well as for other parts with generic specification MIL-PRF-38535 is MIL-STD-883 Method 2009.

When performing external visual inspection in these types, RT FPGAs, there are some tips that have to be considered in addition in order to identify correct results of the inspections.

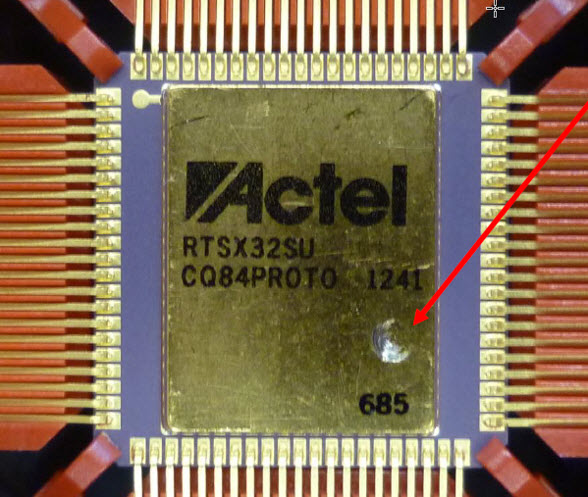

Mark in the top lid in Proto units:

Proto units have a visible mark on the package lid to be well identifiable that those units are not for flight use.

This mark is performed by the manufacturer.

This mark does not affect hermeticity.

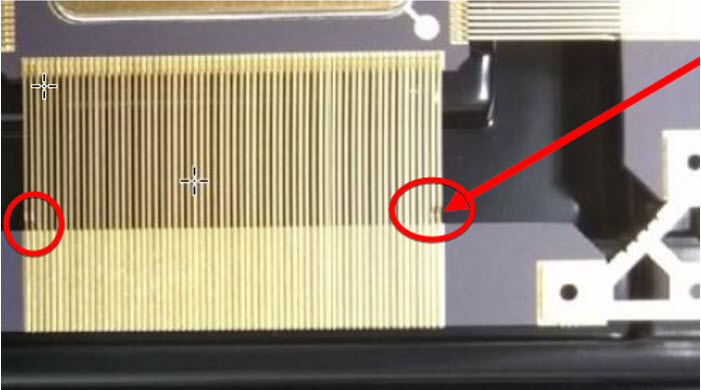

Notch located on lead frame side:

This notch is the result of restraining of the leads done at last production step to guarantee proper planarity for programming.

It will not affect in the process of leads cut and forming.

Bent lead:

Bended lead as seen in the picture is caused by mis-handling of devices.

Before using this part it is needed to restrain the leads otherwise would cause problems in programming, correct sitting in sockets or tooling for lead cut and forming.

Narrow your search of FPGA manufactured by MICROSEMI SOC A MICROCHIP COMPANY just filtering by the proper parameter: quality level, package, equivalent system gates, programming type,…

Antonio Rodríguez Arenas

Antonio is a General Product Assurance expert at Alter Technology with a Degree in Industrial Electronics. Since 1995, he has worked in the Space EEE sector across roles including Project Manager, proposal preparation, and contract negotiation. In recent years, he has specialized in EEE Space Procurement Quality, covering ECSS and DLA standards, ESA alerts, failure analysis, NCR management, and quality assurance for EEE parts in space projects.