| REVISIONS |                                                                                                                                                                        |                 |              |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|--|--|--|--|

| LTR       | DESCRIPTION                                                                                                                                                            | DATE (YR-MO-DA) | APPROVED     |  |  |  |  |

| А         | Make correction to the Output voltage differential test unit from "V" to "mV" as specified under Table I ro                                                            | 14-12-02        | C. SAFFLE    |  |  |  |  |

| В         | Add device type 02 and Single event phenomenon (SEP) requirements. Delete subgroup 9 from Group E end point electrical parameters as specified under Table IIA ro      | 16-09-27        | C. SAFFLE    |  |  |  |  |

| С         | Make change to the Input resistance, differential mode minimum limits by deleting 100 $\Omega$ and replace with 90 $\Omega$ as specified under Table I ro              | 17-06-21        | C. SAFFLE    |  |  |  |  |

| D         | Add paragraph 2.2 for ASTM F1192 guide which covers the Single Event Phenomena (SEP) requirements. Update document paragraphs to current MIL-PRF-38535 requirements ro | 22-07-26        | J. ESCHMEYER |  |  |  |  |

| Revision Status of Sheets                    |                    |                |              |     |    |                                 |               |         |   |    |                                                                                     |    |    |    |    |    |    |    |  |  |  |

|----------------------------------------------|--------------------|----------------|--------------|-----|----|---------------------------------|---------------|---------|---|----|-------------------------------------------------------------------------------------|----|----|----|----|----|----|----|--|--|--|

| REV                                          |                    |                |              |     |    |                                 |               |         |   |    |                                                                                     |    |    |    |    |    |    |    |  |  |  |

| SHEET                                        |                    |                |              |     |    |                                 |               |         |   |    |                                                                                     |    |    |    |    |    |    |    |  |  |  |

| REV                                          | D                  | D              | D            | D   | D  | D                               | D             | D       | D | D  | D                                                                                   | D  | D  | D  | D  | D  | D  | D  |  |  |  |

| SHEET                                        | 1                  | 2              | 3            | 4   | 5  | 6                               | 7             | 8       | 9 | 10 | 11                                                                                  | 12 | 13 | 14 | 15 | 16 | 17 | 18 |  |  |  |

| PMIC N/A                                     |                    | •              |              |     |    |                                 |               |         |   |    |                                                                                     |    |    | •  |    | -  | •  |    |  |  |  |

| MICF                                         | AND<br>ROCI<br>RAW | RCL            | JIT          |     | CH | EPAR<br>ICK O<br>IECKE<br>AJESH | FFICE<br>D BY | R       |   |    | DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990 https://www.dla.mil/LandandMaritime |    |    |    |    |    |    |    |  |  |  |

| THIS DRAV<br>FOR USE BY<br>AND AG<br>DEPARTM | ALL E              | DEPAR<br>ES OF | RTMEI<br>THE | NTS | С  |                                 | ES F. S       | SAFFL   |   | Ē  | MICROCIRCUIT, LINEAR, HIGH SPEED<br>ECL CLOCK / DATA BUFFER, MONOLITHIC             |    |    |    |    |    |    |    |  |  |  |

| DEPARTIV                                     | IENI (             | JF DE          | LEINO        | Е   |    |                                 | 14-           | 10-28   |   |    | SILICON                                                                             |    |    |    |    |    |    |    |  |  |  |

| ļ                                            | AMSC               | N/A            |              |     | RE | VISIO                           |               | EL<br>D |   |    | SIZE CAGE CODE 67268 5962-13205                                                     |    |    |    |    |    |    |    |  |  |  |

|                                              |                    |                |              |     | •  |                                 |               |         |   |    | SHEE                                                                                | ĒΤ | 1  | OF | 18 |    |    |    |  |  |  |

### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device class Q) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

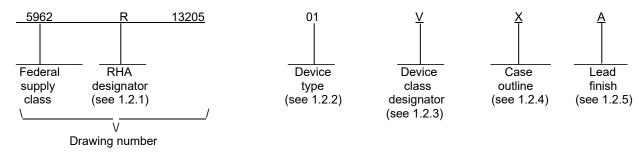

- 1.2 PIN. The PIN is as shown in the following example:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number       | <u>Circuit function</u>                                                                                               |  |  |

|-------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| 01<br>02    | ADCLK925<br>ADCLK925 | High speed emitter coupled logic (ECL) clock / data buffer High speed emitter coupled logic (ECL) clock / data buffer |  |  |

1.2.3 Device class designator. The device class designator is a single letter identifying the product assurance level as follows:

Device class

Device requirements documentation

Q or V

Certification and qualification to MIL-PRF-38535

1.2.4 <u>Case outline(s)</u>. The case outline(s) are as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| Х              | CDFP4-F16              | 16               | Flat pack     |

1.2.5 Lead finish. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V.

| STANDARD             |  |  |  |  |  |

|----------------------|--|--|--|--|--|

| MICROCIRCUIT DRAWING |  |  |  |  |  |

|                      |  |  |  |  |  |

DLA LAND AND MARITIME COLUMBUS, OHIO 43218-3990

| SIZE<br><b>A</b> |                            | 5962-13205 |

|------------------|----------------------------|------------|

|                  | REVISION LEVEL<br><b>D</b> | SHEET 2    |

## 1.3 Absolute maximum ratings. 1/

| Positive supply voltage (VCC) – negative supply voltage (VEE)                   | 6.0 V                      |

|---------------------------------------------------------------------------------|----------------------------|

| Inputs D1, D1                                                                   | VEE – 0.5 V to VCC + 0.5 V |

| Inputs D1, $\overline{D1}$ to center tap (VT) pin :                             |                            |

| (Current mode logic (CML) or positive emitter coupled logic (PECL) termination) |                            |

| Inputs D1 to D1                                                                 | ±1.8 V                     |

| Maximum voltage on output pins                                                  |                            |

| Maximum output current                                                          |                            |

| Input termination, V <sub>T</sub> to D1, $\overline{\text{D1}}$                 |                            |

| Voltage reference (VREF)                                                        |                            |

| Power dissipation (PD)                                                          | 380 mW                     |

| Operating junction temperature (TJ)                                             | 150°C                      |

| Storage temperature range (TSTG)                                                | -65°C to +150°C            |

| Thermal resistance, junction to case ( $\theta$ JC)                             | 125°C/W <u>2</u> /         |

| Thermal resistance, junction to ambient (θJA)                                   | 132°C/W <u>2</u> /         |

| 1.4 Recommended operating conditions.                                           |                            |

| Positive supply voltage (VCC) – negative supply voltage (VEE)                   | 3.3 V                      |

| Ambient operating temperature range (TA)                                        | -55°C to +125°C            |

| 1.5 Operating performance characteristics.                                      |                            |

Unless otherwise specified, TA = +25°C, VCC = VEE = 3.3 V, output terminated to 50  $\Omega$  to (VCC – 2.0 V).

| Input capacitance (CIN) – pins D1, $\overline{D1}$ | 1.0 pF                |            |

|----------------------------------------------------|-----------------------|------------|

| Propagation delay temperature coefficient          | 50 fs/°C              |            |

| Propagation delay skew (output to output)          | 10 ps maximum         |            |

| Random jitter                                      | 60 fs rms maximum     | 3/         |

| Power supply rejection                             |                       |            |

| Output Swing supply rejection                      |                       |            |

| Toggle rate Vop differential at 7.5 GHz            | 0.45 VPP differential | <u>6</u> / |

- 1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2/ Measurement taken under absolute worst case conditions. Data taken with a thermal camera for highest power density location. See MIL-STD-1835 for average package 0JC thermal numbers.

- 3/ VID = 1600 mV, 8 V/ns, VICM = 1.85 V.

- $\underline{4}$ / Change in tPD per change in VCC, VCC VEE = 3.0V =  $\pm$  20%.

- 5/ Change in output swing per change in VCC, VCC VEE = 3.0V =  $\pm$  20%.

- 6/ VPP differential is VOD maximum VOD minimum, which is VPP as measured by a differential probe.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET 3    |

## 1.5 Operating performance characteristics - continued.

Unless otherwise specified, TA = +25°C, VCC = VEE = 3.3 V, output terminated to 50  $\Omega$  to (VCC – 2.0 V).

| Additive phase noise:       |    |      |        |

|-----------------------------|----|------|--------|

| at 622.08 MHz, 10 Hz offset |    | -138 | dBc/Hz |

| at 622.08 MHz, 100 Hz offse | et | -144 | dBc/Hz |

| at 622.08 MHz, 1 kHz offset |    | -152 | dBc/Hz |

| at 622.08 MHz, 10 kHz offse | t  | -159 | dBc/Hz |

| at 622.08 MHz, 100 kHz offs | et | -161 | dBc/Hz |

| at 622.08 MHz, >1 MHz offse | et | -161 | dBc/Hz |

| at 122.88 MHz, 10 Hz offset |    | -135 | dBc/Hz |

| at 122.88 MHz, 100 Hz offse | et | -145 | dBc/Hz |

| at 122.88 MHz, 1 kHz offset |    | -153 | dBc/Hz |

| at 122.88 MHz, 10 kHz offse | t  | -160 | dBc/Hz |

| at 122.88 MHz, 100 kHz offs | et | -161 | dBc/Hz |

| at 122.88 MHz, >1 MHz offse | et | -161 | dBc/Hz |

|                             |    |      |        |

## 1.6 Radiation features.

## Device type 01:

Device type 02:

Single event phenomenon (SEP):

No single event latchup (SEL) occurs at effective linear energy transfer (LET) (see 4.4.4.2):

Device types 01 and 02 ...... ≤ 80 MeV/(mg/cm<sup>2</sup>) 9/

<sup>9/</sup> Limits are characterized at initial qualification and after any design or process changes that may affect the SEP characteristics, but are not production lot tested unless specified by the customer through the purchase order or contract. For more information on single event effect (SEE) test results, customers are requested to contact the manufacturer.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET 4    |

Device type 01 may be dose rate sensitive in a space environment and may demonstrate enhanced low dose rate effects. Radiation end point limits for the noted parameters are guaranteed only for the conditions specified in MIL-STD-883, method 1019, condition A.

<sup>8/</sup> For device type 02, radiation end point limits for the noted parameters are guaranteed for the conditions specified in MIL-STD-883, method 1019, condition D.

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

## DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

## DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at https://quicksearch.dla.mil/.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### ASTM INTERNATIONAL (ASTM)

ASTM F1192 - Standard Guide for the Measurement of Single Event Phenomena (SEP) Induced by Heavy Ion Irradiation of semiconductor Devices.

(Copies of these documents are available online at https://www.astm.org.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

# 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 3.2.1 Case outline. The case outline shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

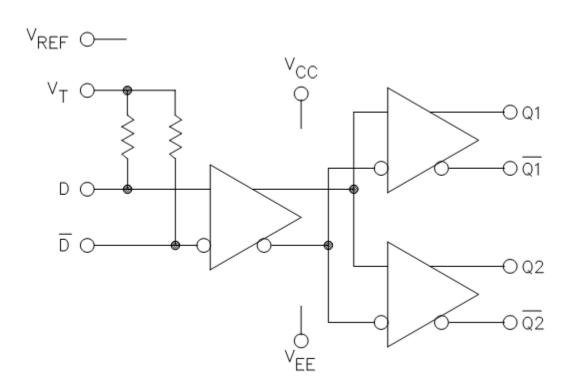

- 3.2.3 Block diagram. The block diagram shall be as specified on figure 2.

- 3.2.4 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table IA and shall apply over the full ambient operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table IA.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET 5    |

# TABLE IA. Electrical performance characteristics.

| Test                              | Symbol | Conditions <u>1</u> / <u>2</u> / <u>3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C | Group A subgroups | Device<br>type | L            | imits        | Unit |

|-----------------------------------|--------|--------------------------------------------------------------------------------|-------------------|----------------|--------------|--------------|------|

|                                   |        | VCC – VEE = 3.3 V,<br>unless otherwise specified                               |                   |                | Min          | Max          |      |

| DC input characteristics section. |        |                                                                                | 1                 | 1              |              | T            | 1    |

| Input voltage high level          | VIH    | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing                 | 1,2,3             | 01, 02         | VEE +<br>1.6 | Vcc          | V    |

|                                   |        | VID = VIH – VIL,  VIH, VIL applied during VOH,  VOL, VOD testing, D,P,L,R      | 1                 | 01             | VEE +<br>1.6 | Vcc          |      |

|                                   |        | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing, D,P,L          | 1                 | 02             | VEE +<br>1.6 | Vcc          |      |

| Input voltage low level           | VIL    | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing                 | 1,2,3             | 01, 02         | VEE          | VCC -<br>0.7 | V    |

|                                   |        | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing, D,P,L,R        | 1                 | 01             | VEE          | VCC -<br>0.7 |      |

|                                   |        | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing, D,P,L          | 1                 | 02             | VEE          | VCC -<br>0.7 |      |

| Input differential range          | VID    | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing                 | 1,2,3             | 01, 02         | 0.2          | 2.8          | VP-P |

|                                   |        | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing, D,P,L,R        | 1                 | 01             | 0.2          | 2.8          |      |

|                                   |        | VID = VIH – VIL, VIH, VIL applied during VOH, VOL, VOD testing, D,P,L          | 1                 | 02             | 0.2          | 2.8          |      |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET 6    |

${\sf TABLE\ IA.\ } \underline{\sf Electrical\ performance\ characteristics} \text{ - Continued.}$

| Test                             | Symbol        | Conditions <u>1</u> / <u>2</u> / <u>3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C | Group A subgroups | Device<br>type | L<br>         | imits         | Unit |

|----------------------------------|---------------|--------------------------------------------------------------------------------|-------------------|----------------|---------------|---------------|------|

|                                  |               | VCC – VEE = 3.3 V, unless otherwise specified                                  |                   |                | Min           | Max           |      |

| DC input characteristics section | n - continued | I                                                                              |                   |                |               |               |      |

| Input current, D, D1             | lih, lil      | Open VT                                                                        | 1,2,3             | 01, 02         |               | 100           | μА   |

|                                  |               | Open VT, D,P,L,R                                                               | 1                 | 01             |               | 100           |      |

|                                  |               | Open VT, D,P,L                                                                 | 1                 | 02             |               | 100           |      |

| Input resistance,                | RIN           |                                                                                | 1,2,3             | 01, 02         | 45            | 58            | Ω    |

| single ended mode                |               | D,P,L,R                                                                        | 1                 | 01             | 45            | 58            |      |

|                                  |               | D,P,L                                                                          | 1                 | 02             | 45            | 58            |      |

| Input resistance,                | RIND          |                                                                                | 1,2,3             | 01, 02         | 90            | 110           | Ω    |

| differential mode                |               | D,P,L,R                                                                        | 1                 | 01             | 90            | 110           |      |

|                                  |               | D,P,L                                                                          | 1                 | 02             | 90            | 110           |      |

| DC output characteristics.       |               |                                                                                |                   |                |               |               |      |

| Output voltage high level        | Voн           | 4/                                                                             | 1,2               | 01, 02         | Vcc -<br>1.26 | Vcc -<br>0.76 | V    |

|                                  |               |                                                                                | 3                 |                | Vcc -<br>1.29 | Vcc -<br>0.76 |      |

|                                  |               | D,P,L,R <u>4</u> /                                                             | 1                 | 01             | Vcc -<br>1.26 | Vcc -<br>0.76 |      |

|                                  |               | D,P,L <u>4</u> /                                                               | 1                 | 02             | VCC -<br>1.26 | VCC -<br>0.76 |      |

| Output voltage low level         | VoL           | 4/                                                                             | 1,2,3             | 01, 02         | VCC -<br>1.99 | VCC -<br>1.54 | V    |

|                                  |               | D,P,L,R <u>4</u> /                                                             | 1                 | 01             | Vcc -<br>1.99 | Vcc -<br>1.54 |      |

|                                  |               | D,P,L <u>4</u> /                                                               | 1                 | 02             | VCC -<br>1.99 | VCC -<br>1.54 |      |

| Output voltage differential      | Vod           | 4/                                                                             | 1,2,3             | 01, 02         | 610           | 1040          | mV   |

|                                  |               | D,P,L,R <u>4</u> /                                                             | 1                 | 01             | 610           | 1040          |      |

|                                  |               | D,P,L <u>4</u> /                                                               | 1                 | 02             | 610           | 1040          | 1    |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205     |

|----------------------------------------------------|------------------|----------------------------|----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>7</b> |

# ${\sf TABLE\ IA.\ } \underline{\sf Electrical\ performance\ characteristics} \text{ - Continued.}$

| Test                        | Symbol                          | Conditions <u>1</u> / <u>2</u> / <u>3</u> /<br>-55°C ≤ TA ≤ +125°C | Group A subgroups | Device<br>type | Limits   |      | Unit |

|-----------------------------|---------------------------------|--------------------------------------------------------------------|-------------------|----------------|----------|------|------|

|                             |                                 | VCC – VEE = 3.3 V,<br>unless otherwise specified                   |                   |                | Min      | Max  |      |

| DC output characteristics - | conti nued.                     |                                                                    |                   |                |          |      |      |

| Reference voltage,          | VREF                            | IREF = 500 μA                                                      | 1                 | 01, 02         | 2.14     | 2.29 | V    |

| output voltage              |                                 |                                                                    | 2                 | ]              | 2.05     | 2.35 | ]    |

|                             |                                 |                                                                    | 3                 |                | 2.10     | 2.40 |      |

|                             |                                 | IREF = 500 μA, D,P,L,R                                             | 1                 | 01             | 2.14     | 2.29 |      |

|                             |                                 | IREF = 500 μA, D,P,L                                               | 1                 | 02             | 2.14     | 2.29 | 1    |

|                             |                                 | IREF = -500 μA                                                     | 1                 | 01, 02         | 1.90     | 2.05 | 1    |

|                             |                                 |                                                                    | 2                 |                | 1.80     | 2.10 | 1    |

|                             |                                 |                                                                    | 3                 | 1              | 1.85     | 2.15 | 1    |

|                             |                                 | IREF = -500 μA, D,P,L,R                                            | 1                 | 01             | 1.90     | 2.05 | 1    |

|                             |                                 | IREF = -500 μA, D,P,L                                              | 1                 | 02             | 1.90     | 2.05 | 1    |

| Reference voltage,          | RREF                            | RREF = VREF / IREF,                                                | 1,2,3             | 01, 02         | 170      | 280  | Ω    |

| output resistance           |                                 | IREF = ±500 μA                                                     |                   |                | 1        |      |      |

|                             |                                 | RREF = VREF / IREF,                                                | 1                 | 01             | 170      | 280  | 1    |

|                             |                                 | IREF = ±500 μA, D,P,L,R                                            |                   |                |          |      |      |

|                             |                                 | RREF = VREF / IREF,                                                | 1                 | 02             | 170      | 280  | 1    |

|                             |                                 | IREF = ±500 μA, D,P,L                                              |                   | '              | <u> </u> |      |      |

| AC performance section.     |                                 |                                                                    |                   |                |          |      |      |

| Propagation delay           | tpD                             | Vcc = 3.3 V ±10%, <u>5</u> /                                       | 9,10,11           | 01, 02         | 190      | 290  | ps   |

|                             |                                 | VICM = VREF, VID = 0.5 VP-P                                        |                   | '              |          |      |      |

| Toggle rate                 | fmin                            | <u>6</u> /                                                         | 4,5,6             | 01, 02         | 5        |      | GHz  |

|                             |                                 | > 0.6 V differential output <u>5</u> /                             |                   |                | 5        |      | 1    |

|                             |                                 | swing, VCC = 3.3 V ±10%                                            |                   |                |          |      |      |

|                             |                                 | > 0.5 V differential output <u>5</u> /                             |                   |                | 7        |      |      |

|                             |                                 | swing, VCC = 3.3 V ±10 %                                           |                   |                |          |      |      |

| Rise / fall time            | t <sub>R</sub> / t <sub>F</sub> | Measured 20% to 80% <u>5</u> /                                     | 9,10,11           | 01, 02         | 30       | 85   | ps   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET 8    |

## TABLE IA. Electrical performance characteristics - Continued.

| Test                    | Symbol | Conditions <u>1</u> / <u>2</u> / <u>3</u> /<br>-55°C ≤ T <sub>A</sub> ≤ +125°C | Group A subgroups | Device<br>type | L   | ₋imits | Unit |

|-------------------------|--------|--------------------------------------------------------------------------------|-------------------|----------------|-----|--------|------|

|                         |        | VCC – VEE = 3.3 V,<br>unless otherwise specified                               |                   |                | Min | Max    |      |

| Power supply section.   |        |                                                                                |                   |                |     |        |      |

| Negative supply current | IVEE   | VCC - VEE = 3.3 V ±10%                                                         | 1,2,3             | 01, 02         | -51 |        | mA   |

|                         |        | VCC - VEE = 3.3 V ±10%,<br>D,P,L,R                                             | 1                 | 01             | -51 |        |      |

|                         |        | VCC - VEE = 3.3 V ±10%,<br>D,P,L                                               | 1                 | 02             | -51 |        |      |

| Positive supply current | IVcc   | VCC - VEE = 3.3 V ±10%                                                         | 1,2,3             | 01, 02         |     | 97     | mA   |

|                         |        | VCC - VEE = 3.3 V ±10%,<br>D,P,L,R                                             | 1                 | 01             |     | 97     |      |

|                         |        | VCC - VEE = 3.3 V ±10%,<br>D,P,L                                               | 1                 | 02             |     | 97     |      |

- Device type 01 supplied to this drawing has been characterized through all levels P, L, R of irradiation and tested at the "P, L and R" levels. Device type 02 has been characterized through levels P and L and is tested at the "L" level. Pre and Post irradiation values are identical unless otherwise specified in Table IA. When performing post irradiation electrical measurements for any RHA level, TA = +25°C.

- 2/ Device type 01 may be dose rate sensitive in a space environment and may demonstrate enhanced low dose rate effects. Radiation end point limits for the noted parameters are guaranteed only for the conditions specified in MIL-STD-883, method 1019, condition A for device type 01 and condition D for device type 02. Device type 02 has been tested at low dose rate.

- 3/ Unless otherwise specified, VCC VEE = 3.3 V. Outputs terminated to 50  $\Omega$  to (VCC 2.0 V).

- 4/ This test is terminated to 50  $\Omega$  to (VCC 2.0 V). Tested at (VCC, VIH,VIL): (3.3, 3.3, 0.0); (3.3, 1.75, 1.55); (2.5, 2.5, 0.0); (2.5, 1.35, 1.15); (2.375, 2.375, 0.0), (2.375, 1.73,1.53), (3.63, 1.9, 1.7).

- 5/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots. Parameter not tested post radiation.

- 6/ Functional automatic test equipment (ATE) production using nominal: VCC / VEE = 3.3 / 0.0 V, 50  $\Omega$  to 1.3 V termination, VID = 800 mV differential input swing. Detection level for VOD > 712 mV differential output swing (-5.0 dBm).

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205     |

|----------------------------------------------------|------------------|----------------------------|----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>9</b> |

## TABLE IB. SEP test limits. 1/

| Device types | SEP    | Temperature<br>TC | Bias Vs | Linear energy transfer (LET)        |

|--------------|--------|-------------------|---------|-------------------------------------|

| 01, 02       | No SEL | +125°C            | +4 V    | LET≤ 80 MeV / (cm/mg <sup>2</sup> ) |

- 1/ For single event phenomena (SEP) test conditions, see 4.4.4.2 herein.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). The certificate of compliance submitted to DLA Land and Maritime-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

## 4. VERIFICATION

- 4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

- 4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

- 4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>10</b> |

| Device types    | 01, 02             |  |  |

|-----------------|--------------------|--|--|

| Case outline    | X                  |  |  |

| Terminal number | Terminal<br>symbol |  |  |

| 1               | VREF               |  |  |

| 2               | VT                 |  |  |

| 3               | D                  |  |  |

| 4               | D                  |  |  |

| 5               | NC/GND             |  |  |

| 6               | NC/GND             |  |  |

| 7               | NC/GND             |  |  |

| 8               | NC/GND             |  |  |

| 9               | VEE                |  |  |

| 10              | Vcc                |  |  |

| 11              | Q2                 |  |  |

| 12              | Q2                 |  |  |

| 13              | Q1                 |  |  |

| 14              | Q1                 |  |  |

| 15              | Vcc                |  |  |

| 16              | VEE                |  |  |

FIGURE 1. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>11</b> |

| Terminal symbol | Description                                                                       |

|-----------------|-----------------------------------------------------------------------------------|

| D               | Noninverting input.                                                               |

| D               | Inverting input.                                                                  |

| NC/GND          | No internal circuitry connected to NC/GND pins so user may ground pin if desired. |

| VEE             | Negative supply voltage.                                                          |

| Vcc             | Positive supply voltage.                                                          |

| Q2              | Inverting output 2.                                                               |

| Q2              | Noninverting output 2.                                                            |

| Q1              | Inverting output 1.                                                               |

| Q1              | Noninverting output 1.                                                            |

| VREF            | Reference voltage. Reference voltage for biasing ac-coupled inputs.               |

| VT              | Center tap. Center tap of 100 $\Omega$ input resistor.                            |

FIGURE 1. <u>Terminal connections</u> - continued.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>12</b> |

FIGURE 2. <u>Block diagram</u>.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>13</b> |

TABLE IIA. Electrical test requirements.

| Test requirements            | Subgroups           |                                         |  |  |

|------------------------------|---------------------|-----------------------------------------|--|--|

|                              | (in accordance with |                                         |  |  |

|                              | MIL-PRF-38          | MIL-PRF-38535, table III)               |  |  |

|                              | Device              | Device                                  |  |  |

|                              | class Q             | class V                                 |  |  |

| Interim electrical           | 1                   | 1                                       |  |  |

| parameters (see 4.2)         |                     |                                         |  |  |

| Final electrical             | 1,2,3, <u>1</u> /   | 1,2,3, <u>1</u> / <u>2</u> / <u>3</u> / |  |  |

| parameters (see 4.2)         | 4,5,6,9,10,11       | 4,5,6,9,10,11                           |  |  |

| Group A test                 | 1,2,3,4,5,6,        | 1,2,3, <u>2</u> /                       |  |  |

| requirements (see 4.4)       | 9,10,11             | 4,5,6,9,10,11                           |  |  |

| Group C end-point electrical | 1,2,3,4,5,6,        | 1,2,3, <u>2</u> / <u>3</u> /            |  |  |

| parameters (see 4.4)         | 9,10,11             | 4,5,6,9,10,11                           |  |  |

| Group D end-point electrical | 1,2,3,4,5,6,        | 1,2,3, <u>2</u> /                       |  |  |

| parameters (see 4.4)         | 9,10,11             | 4,5,6,9,10,11                           |  |  |

| Group E end-point electrical | 1                   | 1 <u>2</u> /                            |  |  |

| parameters (see 4.4)         |                     |                                         |  |  |

- 1/ PDA applies to subgroup 1.

- 2/ See table IA for parameters tested or characterized for subgroups 4, 5, 6, 9, 10, and 11.

- 3/ Delta limits as specified in table IIB shall be required where specified, and the delta limits shall be computed with reference to the zero hour electrical parameters (see table IA).

TABLE IIB. Burn-in and operating life test delta parameters. TA = +25°C. 1/2/

| Parameters                             | Symbol | Delta limits | Units |

|----------------------------------------|--------|--------------|-------|

| Negative supply current                | IVEE   | ±1           | mA    |

| Positive supply current                | IVcc   | ±1           | mA    |

| Output voltage high level              | Voн    | ±0.05        | V     |

| Output voltage low level               | VoL    | ±0.05        | V     |

| Output voltage differential            | Vod    | ±0.05        | V     |

| Input resistance, single ended mode    | RIN    | ±2           | Ω     |

| Input resistance,<br>differential mode | RIND   | ±2           | Ω     |

- 1/ If device is tested at or below delta limit in table, no deltas are required. Deltas are performed at room temperature.

- 2/ Delta parameters are performed at VCC VEE = 3.3 V.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>14</b> |

- 4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections, and as specified herein.

- 4.4.1 Group A inspection.

- a. Tests shall be as specified in table IIA herein.

- b. Subgroups 7 and 8 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroups 4, 5, 6, 9, 10, and 11 are tested as part of device initial characterization and after design and process changes or with subsequent wafer lots as indicated in table IA.

- 4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.2.1 <u>Additional criteria for device classes Q and V</u>. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- 4.4.3 Group D inspection. The group D inspection end-point electrical parameters shall be as specified in table IIA herein.

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein).

- a. End-point electrical parameters shall be as specified in table IIA herein.

- b. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535 for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table IA at TA = +25°C ±5°C, after exposure, to the subgroups specified in table IIA herein.

- 4.4.4.1 <u>Total dose irradiation testing</u>. Total dose irradiation testing shall be performed in accordance with MIL-STD-883 method 1019, condition A for device type 01 and condition D for device type 02, and as specified herein.

- 4.4.4.2 <u>Single event phenomena (SEP)</u>. When specified in the purchase order or contract, SEP testing shall be performed on class V devices. SEP testing shall be performed on the Standard Evaluation Circuit (SEC) or alternate SEP test vehicle as approved by the qualifying activity at initial qualification and after any design or process changes which may affect the upset or latchup characteristics. Test four devices with zero failures. ASTM F1192 may be used as a guideline when performing SEP testing. The recommended test conditions for SEP are as follows:

- a. The ion beam angle of incidence shall be between normal to the die surface and 60° to the normal, inclusive (i.e. 0∘ ≤ angle ≤ 60°). No shadowing of the ion beam due to fixturing or package related effects is allowed.

- b. The fluence shall be  $\ge 10^7$  ions/cm<sup>2</sup>.

- c. The flux shall be between  $10^2$  and  $10^5$  ions/cm<sup>2</sup>/s.

- d. The particle range shall be  $\geq$  20 microns in silicon.

- e. The test temperature shall be +125°C and the maximum rated operating temperature ±10°C for single event latchup testing.

- f. Bias conditions shall be Vs = +4 V for latchup measurements.

- g. For SEP test limits, see Table IB herein.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>15</b> |

### 5. PACKAGING

5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-PRF-38535 for device classes Q and V.

## 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor prepared specification or drawing.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished using DD Form 1692, Engineering Change Proposal, or email communication.

- 6.3 <u>Record of users</u>. Military and industrial users should inform DLA Land and Maritime when a system application requires configuration control and which SMD's are applicable to that system. DLA Land and Maritime will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DLA Land and Maritime-VA, telephone (614) 692-8108.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DLA Land and Maritime-VA, Columbus, Ohio 43218-3990, or telephone (614) 692-0591.

- 6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-PRF-38535 and MIL-HDBK-1331.

- 6.6 Sources of supply.

- 6.6.1 <u>Sources of supply for device classes Q and V</u>. Sources of supply for device classes Q and V are listed in MIL-HDBK-103 and QML-38535. The vendors listed in MIL-HDBK-103 and QML-38535 have submitted a certificate of compliance (see 3.6 herein) to DLA Land and Maritime-VA and have agreed to this drawing.

- 6.7 <u>Additional information</u>. When applicable, a copy of the following additional data shall be maintained and available from the device manufacturer:

- a. RHA test conditions of SEP.

- b. Occurrence of latchup (SEL).

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>16</b> |

### 6.8 Application notes.

- 6.8.1 Power / ground layout and bypassing. The subject device buffers are designed for very high speed applications. Consequently, high speed design techniques must be used to achieve the specified performance. It is critically important to use low impedance supply planes for both the negative supply (VEE) and the positive supply (VCC) planes as part of a multilayer board. Providing the lowest inductance return path for switching currents ensures the best possible performance in the target application. It is also important to adequately bypass the input and output supplies. A 1  $\mu$ F electrolytic bypass capacitor should be placed within several inches of each power supply pin to ground. In addition, multiple high quality 0.001  $\mu$ F bypass capacitors should be placed as close as possible to each of the VEE and VCC supply pins and should be connected to the GND plane with redundant vias. High frequency bypass capacitors should be carefully selected for minimum inductance and equivalent series resistance (ESR). Parasitic layout inductance should be strictly avoided to maximize the effectiveness of the bypass at high frequencies.

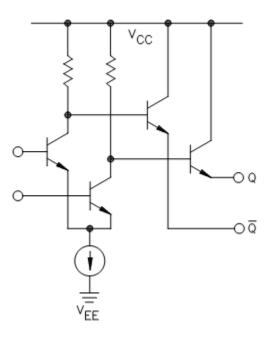

- $6.8.2~\underline{\text{Output stages}}$ . The specified performance can be achieved only by using proper transmission line terminations. The outputs of the buffers are designed to directly drive 800 mV into 50  $\Omega$  cable or microstrip / stripline transmission lines terminated with 50  $\Omega$  referenced to VCC 2 V. The output stage is shown in figure 3. The outputs are designed for best transmission line matching. If high speed signals must be routed more than a centimeter, either the microstrip or the stripline technique is required to ensure proper transition times and to prevent excessive output ringing and pulse width-dependent propagation delay dispersion.

FIGURE 3. Simplified schematic diagram of the output stage.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-13205      |

|----------------------------------------------------|------------------|----------------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>D</b> | SHEET <b>17</b> |

| obtaining the specified performance. Stray can severely limit performance and cause os the specified jitter performance by reducing the specified jitter performance by reducing the lin a 50 $\Omega$ environment, input and output mate termination resistors for both D and D inputs termination potential should be carefully bype to parasitic inductance in the termination return pins are within the rated input differential and termination, but the source must then control There are electrostatic discharge (ESD)/clam | 6.8.3 Optimizing high speed performance. As with any high speed circuit, proper design and layout techniques are essential to obtaining the specified performance. Stray capacitance, inductance, inductive power and ground impedances, or other layout issues can severely limit performance and cause oscillation. Discontinuities along input and output transmission lines can also severely limit he specified jitter performance by reducing the effective input slew rate. In a 50 $\Omega$ environment, input and output matching have a significant impact on performance. The buffer provides internal 50 $\Omega$ ermination resistors for both D and $\overline{D}$ inputs. The return side should normally be connected to the reference pin provided. The ermination potential should be carefully bypassed, using ceramic capacitors to prevent undesired aberrations on the input signal due o parasitic inductance in the termination return path. If the inputs are directly coupled to a source, care must be taken to ensure the poins are within the rated input differential and common-mode ranges. If the return is floated, the device exhibits $100 \Omega$ cross ermination, but the source must then control the common-mode voltage and supply the input bias currents. There are electrostatic discharge (ESD)/clamp diodes between the input pins to prevent the application of excessive offsets to the nput transistors. ESD diodes are not optimized for best ac performance. When a clamp is desired, it is recommended that appropriate external diodes be used. |                                                                      |                                                                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------|--|

| 6.8.4 <u>Buffer random jitter</u> . The device is sperovided sufficient voltage swing is present, recessively large input signals should be clarruns of more than a few centimeters should be                                                                                                                                                                                                                                                                                                                                        | random jitter is affected<br>mped with fast Schottky                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I most by the slew rate of the inputy diodes because attenuators red | ut signal. Whenever possible,<br>uce the slew rate. Input signal |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |                                                                  |  |