|                  |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              | REVIS | SIONS |           |          |    |    |         |        |       |  |

|------------------|------------------|-------|----------------------------|--------|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------|--------------|-------|-------|-----------|----------|----|----|---------|--------|-------|--|

|                  |                  |       |                            |        | LTR                       | LTR DESCRIPTION |                                                                                                                                          |                                                                                          |                                                     |                                      |              | DATE  |       |           | APPROVED |    |    |         |        |       |  |

|                  |                  |       |                            |        | A                         | to 1<br>sec     | Make change to the V <sub>SL(0)</sub> m<br>to 1.26 V as specified under S<br>section of Table I. Update do<br>to current requirements ro |                                                                                          |                                                     | Synchronization<br>cument paragraphs |              |       | 10-18 | C. SAFFLE |          |    |    |         |        |       |  |

|                  |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| Prepared         | in acc           | ordan | ce with                    | n ASMI | E Y14.24                  | 1               |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    | Ve | ndor it | tem dr | awing |  |

| REV              |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| PAGE             |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| REV              |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| PAGE             |                  |       |                            |        |                           |                 |                                                                                                                                          |                                                                                          |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| REV STA          | TATUS REV        |       | s REV A                    |        | A                         | А               | А                                                                                                                                        | Α                                                                                        | А                                                   | Α                                    | А            | А     | А     | Α         | А        | Α  | А  |         |        |       |  |

| OF PAGE          | S                |       | PAG                        | E      | 1                         | 2               | 3                                                                                                                                        | 4                                                                                        | 5                                                   | 6                                    | 7            | 8     | 9     | 10        | 11       | 12 | 13 | 14      |        |       |  |

|                  |                  |       | REPARED BY<br>hu H. Nguyen |        |                           |                 |                                                                                                                                          | DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990<br>http://www.dla.mil/landandmaritime |                                                     |                                      |              |       |       |           |          |    |    |         |        |       |  |

| Original d<br>Yነ | ate of<br>/-MM-I |       | ng                         |        | IECKED BY<br>hu H. Nguyen |                 |                                                                                                                                          |                                                                                          | TITLE<br>- MICROCIRCUIT, LINEAR, 4.5 V TO 60 V WIDE |                                      |              |       |       |           |          | =  |    |         |        |       |  |

|                  |                  |       | PROVED BY<br>homas M. Hess |        |                           |                 | INPUT SYNCHRONOUS PWM BUCK<br>CONTROLLER, MONOLITHIC SILICON                                                                             |                                                                                          |                                                     |                                      |              |       |       | _         |          |    |    |         |        |       |  |

|                  |                  |       | sız<br>A                   |        | ODE ID                    |                 | io.<br>236                                                                                                                               |                                                                                          |                                                     | DWG NO. V62/13607                    |              |       |       |           |          |    |    |         |        |       |  |

|                  |                  |       |                            | REV    |                           |                 | Α                                                                                                                                        |                                                                                          |                                                     |                                      | PAGE 1 OF 14 |       |       |           |          |    |    |         |        |       |  |

|                  |                  |       |                            |        |                           |                 | ~                                                                                                                                        |                                                                                          |                                                     |                                      |              |       | 0.    |           |          |    |    |         |        |       |  |

DISTRIBUTION STATEMENT A. Approved for public release. Distribution is unlimited.

### 1. SCOPE

1.1 <u>Scope</u>. This drawing documents the general requirements of a high performance 4.5 V to 60 V wide input synchronous pulse width modulator (PWM) buck controller microcircuit, with an operating temperature range of -55°C to +125°C.

1.2 <u>Vendor Item Drawing Administrative Control Number</u>. The manufacturer's PIN is the item of identification. The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation:

| <u>V62/13</u>                 | 3607 -                        | <u>01 X</u>                         | Ę                         |                        |

|-------------------------------|-------------------------------|-------------------------------------|---------------------------|------------------------|

| Draw                          |                               | ce type Case out<br>1.2.1) (See 1.2 |                           |                        |

|                               |                               |                                     | (000 1.2.0)               |                        |

| 1.2.1 <u>Device type(s)</u> . |                               |                                     |                           |                        |

| Device type                   | <u>e</u> <u>Generic</u>       |                                     | Circuit function          |                        |

| 01                            | TPS40170 -E                   | P 4.5 V to                          | 60 V wide input synchrono | us PWM buck controller |

| 1.2.2 Case outline(s).        | The case outline(s) are as sp | pecified herein.                    |                           |                        |

| Outline letter                | Number of pins                | JEDEC PUB 95                        | Packad                    | ne style               |

| Outline letter | Number of pins | JEDEC PUB 95 | Package style                 |

|----------------|----------------|--------------|-------------------------------|

| Х              | 20             | JEDEC MO-241 | Plastic quad flatpack no-lead |

1.2.3 Lead finishes. The lead finishes are as specified below or other lead finishes as provided by the device manufacturer:

| Finish designator | Material                 |

|-------------------|--------------------------|

| A                 | Hot solder dip           |

| B                 | Tin-lead plate           |

| C                 | Gold plate               |

| D                 | Palladium                |

| E                 | Gold flash palladium     |

| F                 | Tin-lead alloy (BGA/CGA) |

| Z                 | Other                    |

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/13607 |

|                       |      | REV A          | PAGE 2    |

### 1.3 Absolute maximum ratings. 1/

| Input voltage:                                                        |                                 |

|-----------------------------------------------------------------------|---------------------------------|

| VIN                                                                   | 0.3 V to 62 V                   |

| M/S                                                                   | 0.3 V to VIN                    |

| UVLO                                                                  |                                 |

| SW                                                                    |                                 |

| BOOT                                                                  | V <sub>SM</sub> + 8.8 V maximum |

| Output voltage:                                                       |                                 |

| HDRV                                                                  | . V <sub>SM</sub> to BOOT       |

| BOOT-SW, HDRV-SW (differential from BOOT or HDRV to SW)               | 0.3 V- to 8.8 V                 |

| VBP, LDRV, COMP, RT, ENABLE, PGOOD, SYNC                              | 0.3 V to 8.8 V                  |

| VDD, FB, TRK, SS, ILIM                                                | 0.3 V to 3.6 V                  |

| Grounding:                                                            |                                 |

| AGND-PGND, PGND-AGND                                                  | 200 mV to 200 mV                |

| Power PAD to AGND (must be electrically connected external to device) | . 0 mV                          |

| Electrostatic discharge (ESD):                                        |                                 |

| Human body model (HBM)                                                | . 1.0 kV                        |

| Charged device model (CDM)                                            |                                 |

| Junction temperature range, (TJ)                                      |                                 |

| Storage temperature range, (T <sub>stg</sub> )                        |                                 |

|                                                                       |                                 |

#### 1.4 Recommended operating conditions.

| Input voltage | 1 5 1/    | to 60 | ٧/ |

|---------------|-----------|-------|----|

| input voltage | <br>4.0 V | 10 60 | v  |

### 1.5 Thermal characteristics.

| Thermal metric <u>2</u> /                                                        | Case outline X | Units |

|----------------------------------------------------------------------------------|----------------|-------|

| Junction to ambient thermal resistance, $\theta_{JA}$ <u>3</u> /                 | 35.4           | °C/W  |

| Junction to case (top) thermal resistance, $\theta_{JCtop}$ <u>4</u> /           | 38.1           |       |

| Junction to board thermal resistance, $\theta_{JB}$ <u>5</u> /                   | 10.8           |       |

| Junction to top characterization parameter, $\Psi_{JT}$ <u>6</u> /               | 0.5            |       |

| Junction to board characterization parameter, $\Psi_{JB}$ $\underline{7}/$       | 10.9           |       |

| Junction to case (bottom) thermal resistance, $\theta_{\text{JCbot}}$ <u>8</u> / | 4.3            |       |

<sup>&</sup>lt;u>1</u>/ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

- 2/ For more information about traditional and new thermal metrics, see manufacturer data.

- 3/ The junction to ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K-board, as specified in JESD51-7, in an environment described in JESD51-2a.

- 4/ The junction to case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specified JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- 5/ The junction to board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- 6/ The junction to top characterization parameter, Ψ<sub>JT</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- $\underline{7}$  The junction to board characterization parameter,  $\Psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- 8/ The junction to case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specified JEDEC- standard test exists, but a close description can be found in the ANSI SEMI standard G30-88

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |

|                       |      | REV A          | PAGE 3    |

## 2. APPLICABLE DOCUMENTS

#### AMERICAN NATIONAL STANDARDS INSTITUTE, SEMICONDUCTOR EQUIPMENT and MATERIALS INTERNATIONAL

ANSI SEMI STANDARD G30-88 - Test Method for Junction-to-Case Thermal Resistance Measurements for Ceramic Packages

(Applications for copies should be addressed to the American National Standards Institute, Semiconductor Equipment and Materials International, 1819 L Street, NW, 11 th floor, Washington, DC 20036 or online at <a href="https://www.ansi.org">https://www.ansi.org</a>)

#### JEDEC Solid State Technology Association

| JESD51       | _ | Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device).    |

|--------------|---|-------------------------------------------------------------------------------------------------|

| JESD51-2a    | _ | Integrated Circuits Thermal Test Method Environment Conditions – Natural Convection (Still Air) |

| JESD51-7     | _ | High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages                |

| JESD51-8     | _ | Integrated Circuits Thermal Test Method Environment Conditions – Junction-to-board              |

| JEDEC PUB 95 | - | Registered and Standard Outlines for Semiconductor Devices                                      |

(Applications for copies should be addressed to the JEDEC – Solid State Technology Association, 3103 North 10th Street, Suite 240–S, Arlington, VA 22201-2107.or online at <a href="https://www.jedec.org">https://www.jedec.org</a>).

### 3. REQUIREMENTS

3.1 <u>Marking</u>. Parts shall be permanently and legibly marked with the manufacturer's part number as shown in 6.3 herein and as follows:

- A. Manufacturer's name, CAGE code, or logo

- B. Pin 1 identifier

- C. ESDS identification (optional)

3.2 <u>Unit container</u>. The unit container shall be marked with the manufacturer's part number and with items A and C (if applicable) above.

3.3 <u>Electrical characteristics</u>. The maximum and recommended operating conditions and electrical performance characteristics are as specified in 1.3, 1.4, and table I herein.

- 3.4 Design, construction, and physical dimension. The design, construction, and physical dimensions are as specified herein.

- 3.5 Diagrams.

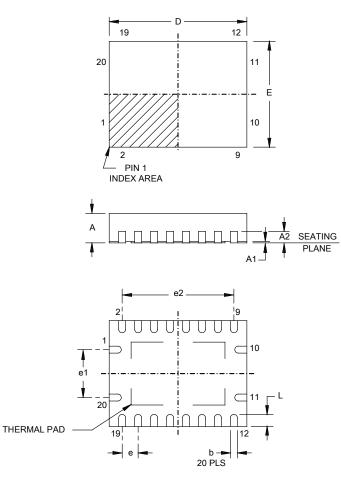

- 3.5.1 Case outline. The case outline shall be as shown in 1.2.2 and figure 1.

- 3.5.2 <u>Terminal connections</u>. The terminal connections shall be as shown in figure 2.

- 3.5.3 <u>Terminal function</u>. The terminal function shall be as shown in figure 3.

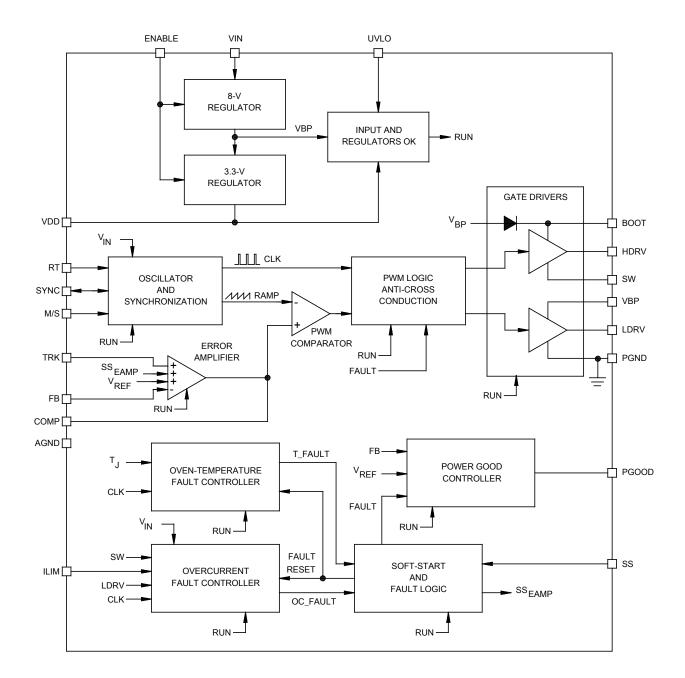

- 3.5.4 <u>Block diagram</u>. The block diagram shall be as shown in figure 4.

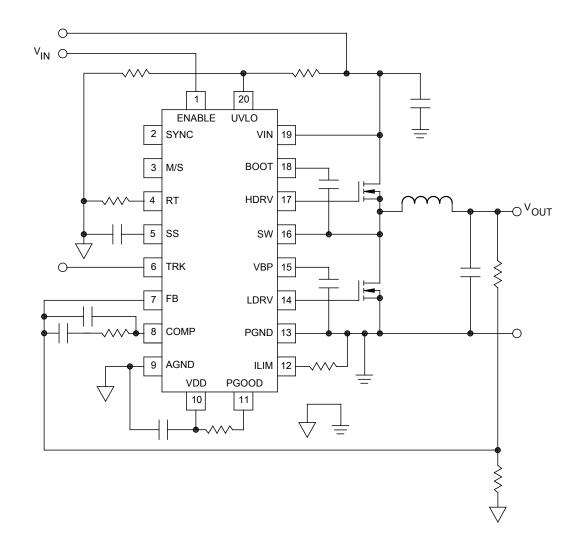

- 3.5.5 <u>Simplified application</u>. The simplified application shall be as shown in figure 5.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13607</b> |

|                       |      | REV A          | PAGE 4           |

# TABLE I. <u>Electrical performance characteristics</u>. <u>1</u>/

| Test                                            | Symbol             | Test conditions                                                                                                                      | Limits |     |      |    |  |

|-------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------|-----|------|----|--|

|                                                 |                    | <u>2</u> /                                                                                                                           | Min    | Тур | Max  |    |  |

| Input supply                                    |                    |                                                                                                                                      |        |     |      |    |  |

| Input voltage range                             | Vvin               |                                                                                                                                      | 4.5    |     | 60   | V  |  |

| Shutdown current                                | I <sub>SD</sub>    | V <sub>ENABLE</sub> < 100 mV                                                                                                         |        | 1   | 2.5  | μA |  |

| Operating current, drives not switching         | Ιαα                | V <sub>ENABLE</sub> ≥ 2 V, f <sub>SW</sub> = 300 kHz                                                                                 |        |     | 4.5  | m/ |  |

| ENABLE                                          | _                  |                                                                                                                                      | 1      |     | 1    |    |  |

| ENABLE pin voltage to disable the device        | V <sub>DIS</sub>   |                                                                                                                                      |        |     | 100  | ۳  |  |

| ENABLE pin voltage to enable the device         | Ven                |                                                                                                                                      | 600    |     |      | _  |  |

| ENABLE pin source current                       | IENABLE            |                                                                                                                                      |        |     | 410  | n/ |  |

| 8-V and 3.3-V regulators                        |                    | L                                                                                                                                    |        |     | I    | 1  |  |

| 8-V regulator output voltage                    | Vvbp               | $V_{\text{ENABLE}} \ge 2 \text{ V}, 8.2 \text{ V} < V_{\text{VIN}} \le 60 \text{ V},$ $0 \text{ mA} < I_{\text{IN}} < 20 \text{ mA}$ | 7.8    | 8.0 | 8.35 | V  |  |

| 8-V regulator dropout voltage, $V_{VIN-VVBP}$   | V <sub>DO</sub>    | 4.5 V < V <sub>VIN</sub> $\leq$ 8.2 V, V <sub>EN</sub> $\geq$ 2 V, I <sub>IN</sub> = 10 mA                                           |        | 110 | 210  | mʻ |  |

| 3.3-V regulator output voltage                  | Vvdd               | $V_{\text{ENABLE}} \ge 2 \text{ V}, 8.2 \text{ V} < V_{\text{VIN}} \le 60 \text{ V},$ $0 \text{ mA} < I_{\text{IN}} < 5 \text{ mA}$  | 3.2    | 3.3 | 3.42 | V  |  |

| Fixed and programmable UVLO                     |                    |                                                                                                                                      |        |     |      |    |  |

| Programmable UVLO ON voltage<br>(at UVLO pin)   | Vuvlo              | V <sub>ENABLE</sub> ≥ 2 V                                                                                                            | 878    | 900 | 920  | m' |  |

| Hysteresis current out of UVLO pin              | Iuvlo              | $V_{\text{ENABLE}} \ge 2 \text{ V}, \text{UVLO pin} > V_{\text{UVLO}}$                                                               | 4.0    | 5   | 6.2  | μA |  |

| VBP turnon voltage                              | VBPON              |                                                                                                                                      | 3.8    |     | 4.4  | V  |  |

| VBP turnoff voltage                             | VBPOFF             | V <sub>ENABLE</sub> ≥ 2 V, UVLO pin > V <sub>UVLO</sub>                                                                              | 3.55   |     | 4.1  |    |  |

| VBP UVLO Hysteresis voltage                     | VBP <sub>HYS</sub> |                                                                                                                                      | 175    |     | 400  | mʻ |  |

| Reference                                       |                    | L                                                                                                                                    |        |     | 1    | 1  |  |

| Reference voltage                               | VREF               | $T_J = 25^{\circ}C, 4.5 \text{ V} < V_{VIN} \le 60 \text{ V}$                                                                        | 594    | 600 | 606  | mʻ |  |

| (+ input of the error amplifier)                |                    | $-55^{\circ}C \le T_{J} \le 125^{\circ}C, \ .4.5 \ V < V_{VIN} \le 60 \ V$                                                           | 585    | 600 | 610  |    |  |

| Oscillator                                      |                    | L                                                                                                                                    |        |     | I    |    |  |

|                                                 |                    | Range (typical)                                                                                                                      | 100    |     | 600  | kH |  |

| Switching frequency                             | fsw                | $R_{RT} = 100 \text{ k}\Omega, 4.5 \text{ V} < V_{VIN} \le 60 \text{ V}$                                                             | 85     | 100 | 115  |    |  |

|                                                 |                    | $R_{RT} = 31.6 \text{ k}\Omega, 4.5 \text{ V} < V_{VIN} \le 60 \text{ V}$                                                            | 270    | 300 | 335  |    |  |

|                                                 |                    | $R_{RT} = 14.3 \text{ k}\Omega, 4.5 \text{ V} < V_{VIN} \le 60 \text{ V}$                                                            | 540    | 600 | 670  |    |  |

| Valley voltage                                  | VVALLEY            |                                                                                                                                      | 0.7    | 1   | 1.25 | V  |  |

| PWM gain (V <sub>VIN</sub> /V <sub>RAMP</sub> ) | K <sub>PWM</sub>   | $4.5 \text{ V} < \text{V}_{\text{VIN}} \le 60 \text{ V}$                                                                             | 14     | 15  | 16   | V/ |  |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/13607 |

|                       |      | REV A          | PAGE 5    |

| Test                                                             | Symbol                         | Test conditions                                                      |      | Limits |      | Unit |

|------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------------|------|--------|------|------|

|                                                                  |                                | <u>2</u> /                                                           | Min  | Тур    | Max  |      |

| PWM and duty cycle                                               | ·                              |                                                                      |      |        |      |      |

| Minimum controlled pulse                                         | t <sub>ON(min)</sub>           | $V_{VIN} \le 4.5 \text{ V}, \text{ f}_{SW} = 300 \text{ kHz}$        |      | 100    | 160  | ns   |

|                                                                  |                                | $V_{VIN} \le 12 \text{ V}, \text{ f}_{SW} = 300 \text{ kHz}$         |      | 75     | 130  |      |

|                                                                  |                                | V <sub>VIN</sub> ≤ 60 V, f <sub>SW</sub> = 300 kHz                   |      | 50     | 80   |      |

| Minimum OFF time                                                 | toff(max)                      | V <sub>VIN</sub> ≤ 12 V, f <sub>SW</sub> = 300 kHz                   |      | 170    | 250  | ns   |

| Maximum duty cycle                                               | D <sub>MAX</sub>               | $f_{SW} = 100 \text{ kHz}, 4.5 \text{ V} < V_{VIN} \le 60 \text{ V}$ | 95%  |        |      | ns   |

|                                                                  |                                | fsw = 300 kHz, 4.5 V < V <sub>VIN</sub> ≤ 60 V                       | 90%  |        |      |      |

|                                                                  |                                | fsw = 600 kHz, 4.5 V < V <sub>VIN</sub> ≤ 60 V                       | 82%  |        |      |      |

| Error amplifier                                                  |                                |                                                                      |      |        |      |      |

| Gain bandwidth product <u>4</u> /                                | GBWP                           |                                                                      | 7    | 10     | 13   | MHz  |

| Open loop gain <u>4</u> /                                        | A <sub>OL</sub>                |                                                                      | 80   | 90     | 95   | dB   |

| Input bias current                                               | IIB                            |                                                                      |      |        | 135  | nA   |

| Output source current                                            | IEAOP                          | V <sub>VFB</sub> = 0 V                                               | 1.8  |        |      | mA   |

| Output sink current                                              | I <sub>EAOM</sub>              | V <sub>VFB</sub> = 1 V                                               | 1.9  |        |      | mA   |

| Programmable soft start                                          |                                | I                                                                    |      | L      | I    |      |

| Soft start source current at $V_{SS}$ < 0.5 V                    | ISS(source,start)              | V <sub>SS</sub> = 0.25 V                                             | 42   | 52     | 62   | μA   |

| Soft start source current at $V_{SS}$ > 0.5 V                    | I <sub>SS(source,normal)</sub> | V <sub>SS</sub> = 1.5 V                                              | 9.2  | 11.6   | 13.9 |      |

| Soft start sink current                                          | ISS(sink)                      | Vss = 1.5 V                                                          | 0.7  | 1.05   | 1.36 |      |

| SS pin HIGH voltage during fault<br>(OC or thermal) reset timing | Vss(fitH)                      |                                                                      | 2.38 | 2.5    | 2.65 | V    |

| SS pin LOW voltage during fault<br>(OC or thermal) reset timing  | VSS(fltL)                      |                                                                      | 235  | 300    | 375  | mV   |

| SS pin voltage during steady state                               | V <sub>SS(steady_state)</sub>  |                                                                      | 3.2  | 3.3    | 3.55 | V    |

| Initial offset voltage from SS pin to error<br>amplifier input   | VSS(offst)                     |                                                                      | 525  | 650    | 790  | mV   |

| Tracking                                                         |                                |                                                                      |      |        |      |      |

| Range of TRK which overrides $V_{REF}$                           | VTRK(ctrl)                     |                                                                      | 0    |        | 600  | mV   |

# TABLE I. Electrical performance characteristics - Continued. 1/

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |

|                       |      | REV A          | PAGE 6    |

| TABLE I. | Electrical performance characteristics - Continued. | <u>1</u> / |

|----------|-----------------------------------------------------|------------|

|----------|-----------------------------------------------------|------------|

| Test                                                                                     | Symbol                      | Test conditions                                                                                     |      | Limits |      | Unit |

|------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------|------|--------|------|------|

|                                                                                          |                             | <u>2</u> /                                                                                          | Min  | Тур    | Max  |      |

| Synchronization (Master/Slave)                                                           |                             |                                                                                                     |      |        |      |      |

| M/S pin voltage in master mode                                                           | V <sub>MSTR</sub>           |                                                                                                     | 3.9  |        | VIN  | V    |

| M/S pin voltage in slave 0° mode                                                         | VSLV(0)                     |                                                                                                     | 1.26 |        | 1.74 | V    |

| M/S pin voltage in slave 180° mode                                                       | VSLV(180)                   |                                                                                                     | 0    |        | 0.74 | V    |

| SYNC pin pulldown current                                                                | I <sub>SYNC(in)</sub>       |                                                                                                     | 8    | 11     | 14.5 | μΑ   |

| SYNC pin input high voltage level                                                        | VSYNC(in_high)              | M/S configured as slave- 0° or                                                                      | 2    |        |      | V    |

| SYNC pin input low voltage level                                                         | VSYNC(in_low)               | slave- 180°                                                                                         |      |        | 0.8  | V    |

| Minimum SYNC high pulse duration                                                         | t <sub>SYNC(high_min)</sub> |                                                                                                     | 40   |        |      | ns   |

| Minimum SYNC low pulse duration                                                          | tsync(low_min)              |                                                                                                     | 40   |        |      | ns   |

| Gate drivers                                                                             |                             |                                                                                                     |      | 1      | 1    |      |

| High side driver pullup resistance                                                       | R <sub>HDHI</sub>           |                                                                                                     | 1.37 | 2.64   | 4    | Ω    |

| High side driver pulldown resistance                                                     | Rhdlo                       | C <sub>LOAD</sub> = 2.2 nF, I <sub>DRV</sub> = 300 mA,<br>T <sub>J</sub> = -55°C to 125°C           | 1    | 2.4    | 4    |      |

| Low side driver pullup resistance                                                        | Rldhi                       |                                                                                                     | 1.25 | 2.4    | 4    |      |

| Low side driver pulldown resistance                                                      | R <sub>LDLO</sub>           |                                                                                                     | 0.44 | 1.1    | 1.7  |      |

| Time delay between HDRV fall and LDRV rise                                               | tNON-OVERLAP1               | $C_{LOAD} = 2.2 \text{ nF}$                                                                         |      | 50     |      | ns   |

| Time delay between HDRV rise and LDRV fall                                               | t <sub>NON-OVERLAP2</sub>   | $V_{HDRV} = 2 V, V_{LDRV} = 2 V$                                                                    |      | 60     |      |      |

| Overcurrent protection (Low-side MOSFET sense                                            | sing)                       | l                                                                                                   |      |        |      | 1    |

| ILIM pin source current                                                                  | IILIM                       | 4.5 V < V <sub>VIN</sub> $\leq$ 60 V, T <sub>J</sub> = 25°C                                         | 9    | 9.75   | 11   | μA   |

|                                                                                          |                             | 4.5 V < V <sub>VIN</sub> $\leq$ 60 V, T <sub>J</sub> = -55°C to 125°C                               | 6.9  |        | 12   |      |

| ILIM pin source current during soft start                                                | I <sub>ILIM,(ss)</sub>      | $4.5 \text{ V} < \text{V}_{\text{VIN}} \le 60 \text{ V}, \text{ T}_{\text{J}} = 25^{\circ}\text{C}$ |      | 15     |      | 1    |

| Temperature coefficient of ILIM current                                                  | IILIM, TC                   | 4.5 V < V <sub>VIN</sub> ≤ 60 V                                                                     |      | 1400   |      | ppm  |

| ILIM pin voltage operating range                                                         | VILIM                       | 4.5 V < V <sub>VIN</sub> ≤ 60 V                                                                     | 50   |        | 300  | mV   |

| Overcurrent protection threshold (voltage across low-side FET for detecting overcurrent) | ОСРтн                       | R <sub>ILIM</sub> = 10 kΩ, I <sub>ILIM</sub> = 10 μA<br>(V <sub>ILIM</sub> = 100 mV)                | -110 | -100   | -84  |      |

See footnote at end of table.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |  |

|                       |      | REV A          | PAGE 7    |  |

| Test                                                                 | Symbol                | Test conditions                                     | Limits |      |      | Unit |

|----------------------------------------------------------------------|-----------------------|-----------------------------------------------------|--------|------|------|------|

|                                                                      |                       | <u>2</u> /                                          | Min    | Тур  | Max  |      |

| Short circuit protection (High side MOSFET sense                     | sing)                 |                                                     |        |      |      |      |

| LDRV pin maximum voltage during calibration                          | VLDRV(max)            | R <sub>LDRV</sub> = open                            |        | 300  | 360  | mV   |

| Multiplier factor to set the SCP based on                            | A <sub>OC3</sub>      | $R_{LDRV} = 10 \ k\Omega$                           | 2.75   | 3.2  | 3.6  | V/V  |

| OCP level setting at the ILIM pin                                    | Aoc7                  | R <sub>LDRV</sub> = open                            | 6.3    | 7.25 | 7.91 |      |

|                                                                      | A <sub>OC15</sub>     | $R_{LDRV} = 20 \ k\Omega$                           | 13.5   | 16.4 | 18   |      |

| Thermal shutdown                                                     | 1                     |                                                     |        | 1    | •    | 1    |

| hermal shutdown set threshold <u>3</u> / T <sub>SD,set</sub>         |                       | 155                                                 | 165    | 175  | °C   |      |

| Thermal shutdown reset threshold <u>3</u> /                          | T <sub>SD,reset</sub> | 4.5 V < V <sub>VIN</sub> ≤ 60 V                     | 125    | 135  | 145  |      |

| Thermal shutdown hysteresis                                          | T <sub>hyst</sub>     | -                                                   |        | 30   |      |      |

| Power Good                                                           |                       | •                                                   |        | 1    |      | 1    |

| FB pin voltage upper limit for power good                            | Vov                   |                                                     | 620    | 647  | 675  | mV   |

| FB pin voltage lower limit for power good                            | Vuv                   | 4.5 V < V <sub>VIN</sub> ≤ 60 V                     | 520    | 552  | 575  |      |

| Power good hysteresis voltage at FB pin                              | Vpg,hyst              | -                                                   | 8.4    | 20   | 33   |      |

| PGOOD pin voltage when FB pin<br>voltage > Vov or < Vuv, IPGD = 2 mA | VPG(out)              |                                                     |        |      | 100  |      |

| PGOOD pin voltage when device power is<br>removed                    | VPG(np)               | $V_{VIN}$ is open, 10-k $\Omega$ to $V_{EXT} = 5 V$ |        | 1    | 1.5  | V    |

| Boot diode                                                           |                       |                                                     |        |      |      |      |

| Bootstrap diode forward voltage                                      | Vdfwd                 | I = 20 mA                                           | 0.5    | 0.7  | 1    | V    |

| Discharge resistor from BOOT to SW                                   | RBOOT-SW              |                                                     |        | 1    |      | MΩ   |

# TABLE I. Electrical performance characteristics - Continued. 1/

1/ Testing and other quality control techniques are used to the extent deemed necessary to assure product performance over the specified temperature range. Product may not necessarily be tested across the full temperature range and all parameters may not necessarily be tested. In the absence of specific parametric testing, product performance is assured by characterization and/or design.

<u>2</u>/ These specifications apply for  $-55^{\circ}C \le T_{J} \le +125^{\circ}C$ ,  $V_{IN} = 12$  V, unless otherwise noted. <u>3</u>/ Ensured by design, not production tested.

$\frac{1}{4}$  Ensured by design at -40°C ≤ T<sub>J</sub> ≤ +125°C, not production test.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.          |

|-----------------------|------|----------------|------------------|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | <b>V62/13607</b> |

|                       |      | REV A          | PAGE 8           |

|        | Dimensions  |      |             |           |        |       |        |

|--------|-------------|------|-------------|-----------|--------|-------|--------|

| Symbol | Millimeters |      | Millimeters |           | Symbol | Milli | meters |

|        | Min         | Max  |             | Min       | Max    |       |        |

| А      | 0.80        | 1.00 | E           | 3.35      | 3.65   |       |        |

| A1     | 0.00        | 0.05 | е           | 0.50 BSC  |        |       |        |

| A2     | 0.20        | TYP  | e1          | 1.50 BSC  |        |       |        |

| b      | 0.18        | 0.30 | e2          | 3.50 BSC  |        |       |        |

| D      | 4.35        | 4.65 | L           | 0.30 0.50 |        |       |        |

### NOTES:

- 1. All linear dimensions are in millimeters.

- 2. his drawing is subject to change without notice.

- 3. QFN (Quad Flatpack No-Lead) package configuration .

- 4. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- 5. See additional figure in the manufacturer's data for details regarding the exposed thermal pad features and dimensions.

- 6. Pin 1 identifiers are located on both top and bottom of the package and within the zone indicated.

- 7. Falls within JEDEC MO-241 variation AB.

FIGURE 1. Case outline.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |

|-----------------------|------|----------------|-----------|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |

|                       |      | REV A          | PAGE 9    |

|                    | Case outline X     |                    |                    |  |  |  |

|--------------------|--------------------|--------------------|--------------------|--|--|--|

| Terminal<br>number | Terminal<br>symbol | Terminal<br>number | Terminal<br>symbol |  |  |  |

| 1                  | ENABLE             | 20                 | UVLO               |  |  |  |

| 2                  | SYNC               | 19                 | VIN                |  |  |  |

| 3                  | M/S                | 18                 | BOOT               |  |  |  |

| 4                  | RT                 | 17                 | HDRV               |  |  |  |

| 5                  | SS                 | 16                 | SW                 |  |  |  |

| 6                  | TRK                | 15                 | VBP                |  |  |  |

| 7                  | FB                 | 14                 | LDRV               |  |  |  |

| 8                  | COMP               | 13                 | PGND               |  |  |  |

| 9                  | AGND               | 12                 | ILIM               |  |  |  |

| 10                 | VDD                | 11                 | PGOOD              |  |  |  |

FIGURE 2. Terminal connections.

| Tern   | ninal  | I/O | Description                                                                                                                                                                                                                                                                                                                                |

|--------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | number |     |                                                                                                                                                                                                                                                                                                                                            |

| AGND   | 9      |     | Analog signal ground. This pin must be electrically connected to power ground PGND externally.                                                                                                                                                                                                                                             |

| BOOT   | 18     | 0   | Boot-capacitor node for high-side FET gate driver. The boot capacitor is connected from this pin to SW.                                                                                                                                                                                                                                    |

| COMP   | 8      | 0   | Output of the internal error amplifier. The feedback loop compensation network is connected from this pin to the FB pin.                                                                                                                                                                                                                   |

| ENABLE | 1      | Ι   | This pin must be high for the device to be enabled. If this pin is pulled low, the device is put in a low-power- consumption shutdown mode.                                                                                                                                                                                                |

| FB     | 7      | Ι   | Negative input to the error amplifier. The output voltage is fed back to this pin through a resistor-<br>divider network.                                                                                                                                                                                                                  |

| HDRV   | 17     | 0   | Gate-driver output for the high-side FET.                                                                                                                                                                                                                                                                                                  |

| ILIM   | 12     | 0   | A resistor from this pin to PGND sets the overcurrent limit. This pin provides source current used for the overcurrent-protection threshold setting.                                                                                                                                                                                       |

| LDRV   | 14     | 0   | Gate driver output for the low-side FET. Also, a resistor from this pin to PGND sets the multiplier factor to determine the short-circuit current limit. If no resistor is present, the multiplier defaults to 7 times the ILIM pin voltage                                                                                                |

| M/S    | 3      | I   | Master- or slave-mode selector pin for frequency synchronization. This pin must be tied to VIN for master mode. In the slave mode, this pin must be tied to AGND or left floating. If the pin is tied to AGND, the device synchronizes with a 180° phase shift. If the pin is left floating, the device synchronizes with a 0° phase shift |

| PGND   | 13     |     | Power ground. This pin must externally connect to the AGND at a single point.                                                                                                                                                                                                                                                              |

| PGOOD  | 11     | 0   | Power-good indicator. This pin is an open-drain output pin, and a $10-k\Omega$ pullup resistor is recommended to be connected between this pin and VDD.                                                                                                                                                                                    |

| RT     | 4      | Ι   | A resistor from this pin to AGND sets the oscillator frequency. Even if operating in slave mode, it is required to have a resistor at this pin to set the free-running switching frequency.                                                                                                                                                |

| SS     | 5      | Ι   | Soft-start. A capacitor must be connected from this pin to AGND. The capacitor value sets the soft-<br>start time.                                                                                                                                                                                                                         |

FIGURE 3. Terminal function.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |  |

|                       |      | REV A          | PAGE 10   |  |

| Terminal I/ |        | I/O | Description – Continued.                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol      | number |     |                                                                                                                                                                                                                                                                                                                |  |  |  |

| SW          | 16     | Ι   | This pin must connect to the switching node of the synchronous buck converter. The high-side and low-side FET current sensing are also done from this node.                                                                                                                                                    |  |  |  |

| SYNC        | 2      | I/O | Synchronization. This is a bidirectional pin used for frequency synchronization. In the master mode, it is the SYNC output pin. In the slave mode, it is a SYNC input pin. If unused, this pin can be left open.                                                                                               |  |  |  |

| TRK         | 6      | Ι   | Tracking. External signal at this pin is used for output voltage tracking. This pin goes directly to the internal error amplifier as a positive reference. The lesser of the voltages between VTRK and the internal 600-mVreference sets the output voltage. If not used, this pin should be pulled up to VDD. |  |  |  |

| UVLO        | 20     | Ι   | Undervoltage lockout. A resistor divider on this pin from VIN to AGND can be used to set the UVLO threshold                                                                                                                                                                                                    |  |  |  |

| VBP         | 15     | 0   | 8-V regulated output for gate driver. A ceramic capacitor with a value between 1 $\mu F$ and 10 $\mu F$ must be connected from this pin to PGND                                                                                                                                                                |  |  |  |

| VDD         | 10     | 0   | 3.3-V regulated output. A ceramic bypass capacitor with a value between 0.1 $\mu$ F and 1 $\mu$ F must be connected between this pin and the AGND pin and placed closely to this pin.                                                                                                                          |  |  |  |

| VIN         | 19     | Ι   | Input voltage for the controller, which is also the input voltage for the dc-dc converter. A 1-µF bypass capacitor from this pin to AGND must be added and placed closed to VIN.                                                                                                                               |  |  |  |

FIGURE 3. <u>Terminal function</u> – Continued.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | 16236          | V62/13607 |  |

|                       |      | REV A          | PAGE 11   |  |

FIGURE 4. Block diagram.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. V62/13607 |  |

|-----------------------|------|----------------|-------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                   |  |

|                       |      | REV A          | PAGE 12           |  |

FIGURE 5. Simplified application.

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO. V62/13607 |  |

|-----------------------|------|----------------|-------------------|--|

| COLUMBUS, OHIO        | A    | 16236          |                   |  |

|                       |      | REV A          | PAGE 13           |  |

## 4. VERIFICATION

4.1 <u>Product assurance requirements</u>. The manufacturer is responsible for performing all inspection and test requirements as indicated in their internal documentation. Such procedures should include proper handling of electrostatic sensitive devices, classification, packaging, and labeling of moisture sensitive devices, as applicable.

### 5. PREPARATION FOR DELIVERY

5.1 <u>Packaging</u>. Preservation, packaging, labeling, and marking shall be in accordance with the manufacturer's standard commercial practices for electrostatic discharge sensitive devices.

## 6. NOTES

6.1 ESDS. Devices are electrostatic discharge sensitive and are classified as ESDS class 1 minimum.

6.2 <u>Configuration control</u>. The data contained herein is based on the salient characteristics of the device manufacturer's data book. The device manufacturer reserves the right to make changes without notice. This drawing will be modified as changes are provided.

6.3 <u>Suggested source(s) of supply</u>. Identification of the suggested source(s) of supply herein is not to be construed as a guarantee of present or continued availability as a source of supply for the item. DLA Land and Maritime maintains an online database of all current sources of supply at <u>https://landandmaritimeapps.dla.mil/programs/smcr/</u>.

| Vendor item drawing<br>administrative control<br>number <u>1</u> / | Device<br>manufacturer<br>CAGE code | Mode of<br>transportation<br>and quantity | Top side<br>marking | Vendor part number |

|--------------------------------------------------------------------|-------------------------------------|-------------------------------------------|---------------------|--------------------|

| V62/13607-01XE                                                     | 01295                               | Tape and reel,<br>250 units               | PZYM                | TPS40170MRGYTEP    |

1/ The vendor item drawing establishes an administrative control number for identifying the item on the engineering documentation.

CAGE code

01295

Source of supply

Texas Instruments, Incorporated Semiconductor Group 8505 Forest Lane P.O. Box 660199 Dallas, TX 75243

| DLA LAND AND MARITIME | SIZE | CODE IDENT NO. | DWG NO.   |  |

|-----------------------|------|----------------|-----------|--|

| COLUMBUS, OHIO        | A    | <b>16236</b>   | V62/13607 |  |

|                       |      | REV A          | PAGE 14   |  |