# Influence of assembly methods and thermal cycling on MLCC capacitors on crack appearance. Microsection study

C. López-López, E. Torres, S. Reina, C. Marcos, M. Dominguez, J.M. Jimenez

TÜV NORD GROUP

# **Multilayer Ceramic Capacitors**

T. Tsurumi & T. Hoshina, .Handbook of Advanced Ceramic, 2013, 415-427 MJ Pan & CA Randall, IEEE Electrical Insularion Magazine, 26 (3), 2010, 44-50.

2 EMPS-10 - 10th Workshop on Electronics Materials & Processes for Space, May 15-16, 2019

•Ceramic capacitors are the most widely used passive component in electronic circuit.

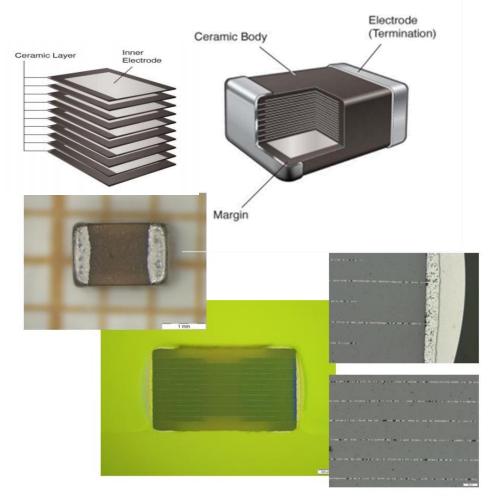

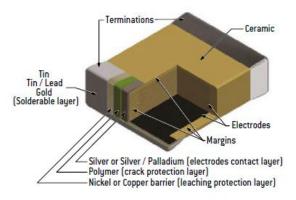

MLCCs are composed of dielectric layers, inner electrodes, and outer terminal electrodes.

•Some MCLL designs add Flexible Terminations to improve the performance of the device.

J. Prymark et al., CARTS USE Proceedings, 29 Passive Components Symposium, 2009.

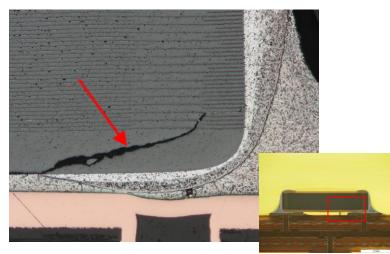

#### Fracture failure on assembled Multilayer Ceramic Capacitors

Cracking is related mostly to the thermal or mechanical stress caused during:

- Handling

- Assembly

- Testing

Some factors that influence on the appearance of cracks during the **assembly process** are:

- Excessive volume of solder

- Impact by mounting machine

- Incorrect heating and cooling process

- Deflexion of sustrate

B. J.AlAhmar, E. Wiss, S. Wiese, IEEE, EurosimE, 2018.

# **Verification Procedure**

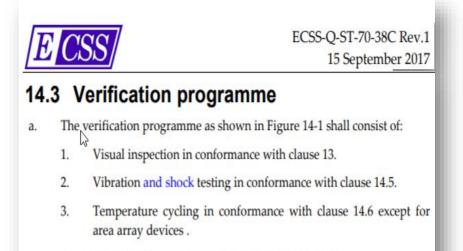

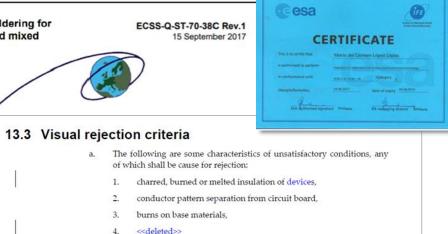

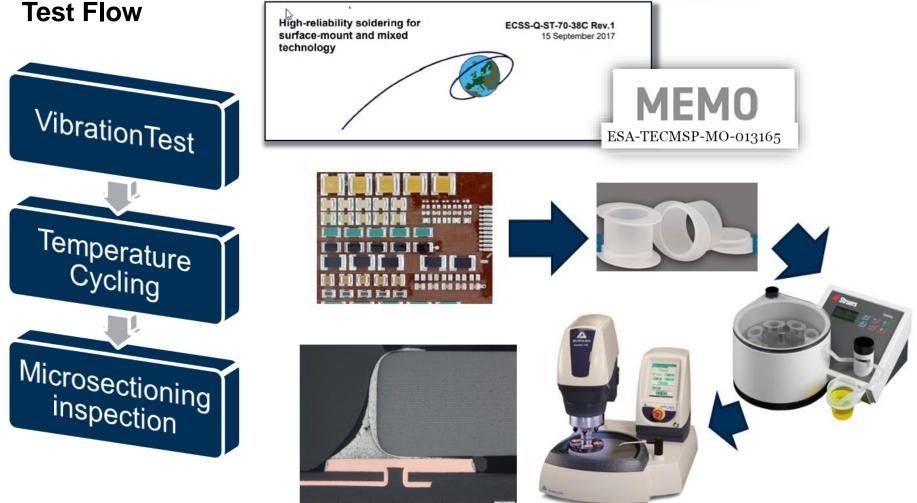

To carry out the microsection the lab have to be certify by the ESA  The soldering verification is performed according to ECSS-Q-ST-70-38C Rev.1, 10C, -12C, -08C, -60C.

> The standards defines the <u>technical</u> requirements and <u>quality</u> assurance provisions

Microsectioning in conformance with clause 14.7.

## **Verification Procedure**

| Date | 7 <sup>th</sup> of March 2019                                                                                                | Ref  | ESA-TECMSP-MO-013165                            |

|------|------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------|

| From | C. Villette Carole Villette Villette Villette                                                                                | Visa | T. Rohr                                         |

| То   | SMT Approved assembly line, ESA PA<br>Managers, ESA skills training school,<br>ESA recommended microsectioning<br>facilities | Сору | G. Corocher, J. Hokka, E. Peraud, S.<br>Heltzel |

#### Subject: ESA recommended microsectioning facilities

The following facilities are ESA recommended for inspection, microsectioning and assessment of the microsectioning of assembled devices mounted on verification boards, having been submitted to a verification programme in compliance with ECSS-Q-ST-70-07C, ECSS-Q-ST-70-08C and ECSS-Q-ST-70-38C.

The competencies of the laboratories have been assessed by ESA in compliance with ESA-TECMSP-MO-013161 (www.escies.org). These companies are considered as Category A as described in the ESA-TECMSP-MO-013162 (www.escies.org).

These companies may also provide expertise in the field of unpopulated Printed Circuit Board microsectioning.

The list of companies is uploaded on the escies website (www.escies.org).

#### Alter Technology TUV

Mr. Manuel Dominguez

# GOALS

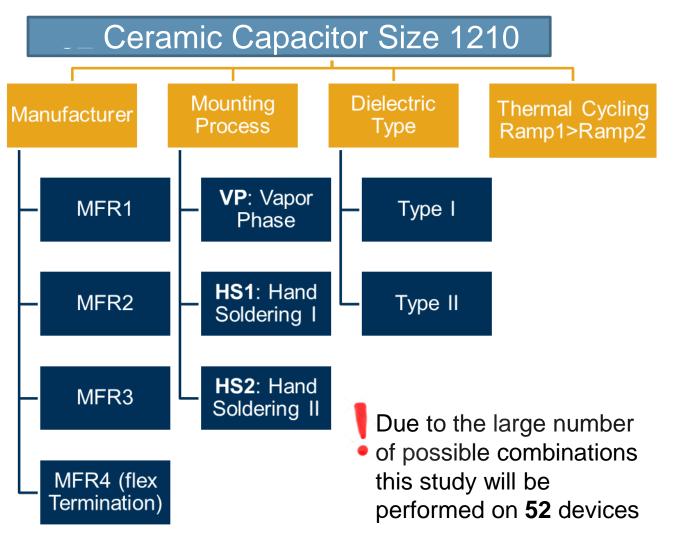

The aim of this study is to asses the susceptibility to cracking of soldered MLCC capacitors, as a function of:

- Manufacturer

- Assembly method

- Dielectric Type

- Thermal cycling conditions

**ThalesAlenia**

a Thales / Leonardo company Space

- excessive solder (including peaks, icicles and bridging), see clause 11.5,

- flux residue, solder splatter, solder balls, or other foreign matter on circuitry, beneath devices or on adjacent areas,

- 7. dewetting,

0.0035

100.00

Frequency (Hz)

2000.02

1000.00

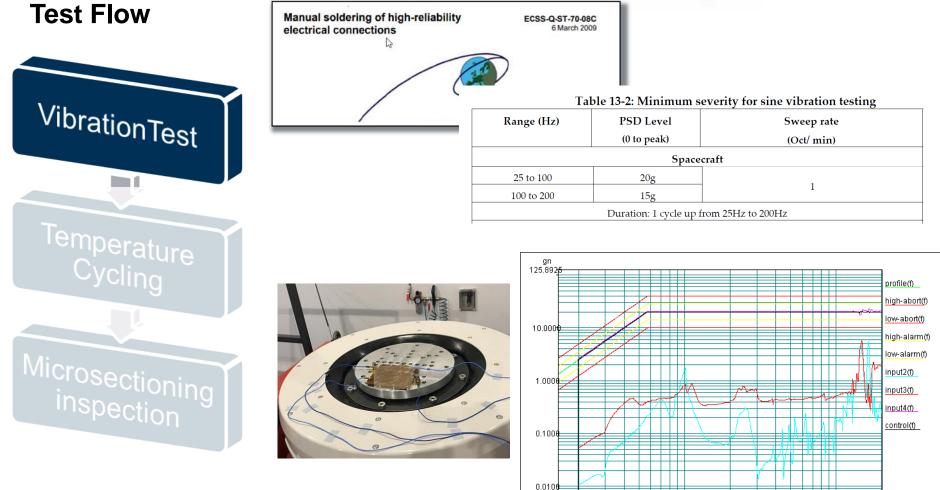

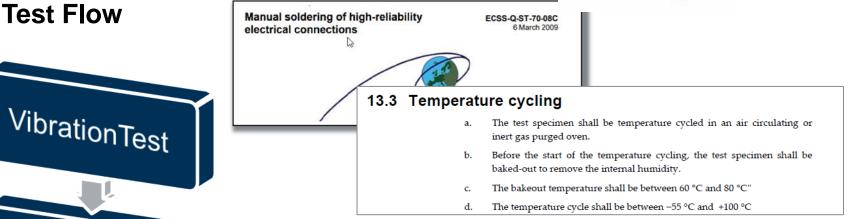

10 EMPS-10 - 10th Workshop on Electronics Materials & Processes for Space, May 15-16, 2019

Temperature

Cycling

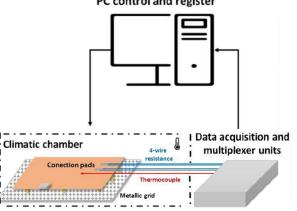

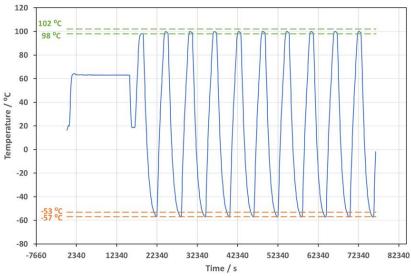

Temperature cycling test is defined by the following parameters: PC control and register

- Baked-out temperature

- Number of cycles

- Max/Min temperature

- Dwell time

- Temperature ramp

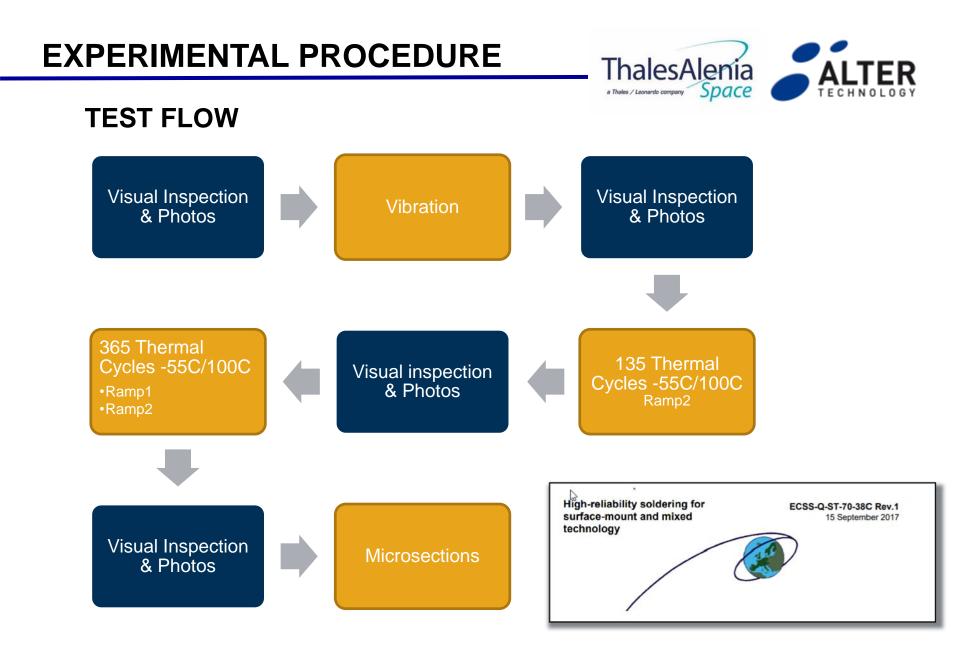

**Test Flow**

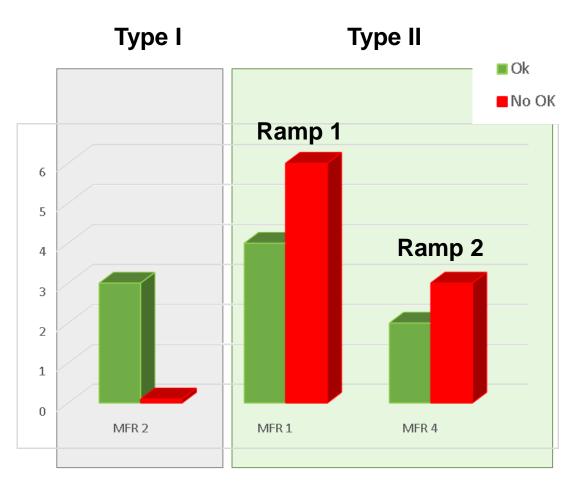

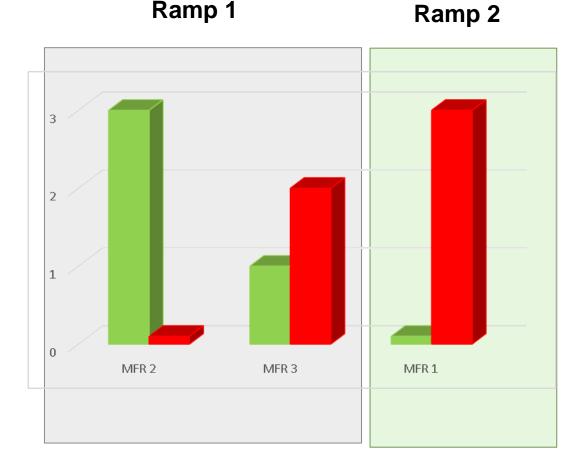

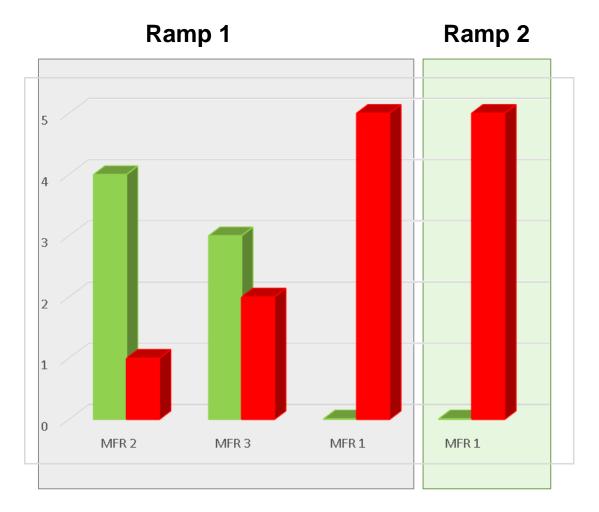

Ramp Temperature Condition:

Ramp 1 > Ramp 2

The temperature profile was monitoring in order to record any deviation:

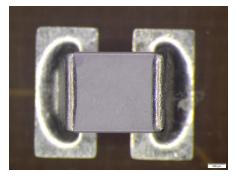

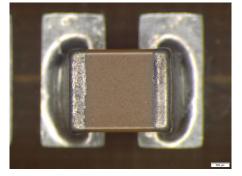

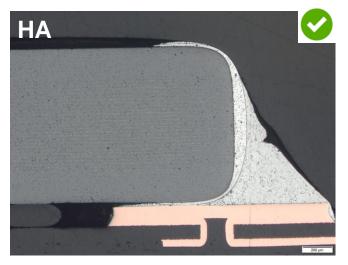

# 52 Ceramic Capacitor Size 1210 **VP**: Vapor Phase **Mounting Process** HS1: Hand Soldering Process I HS2: Hand Soldering Process II **Dielectric Type II Dielectric Type I**

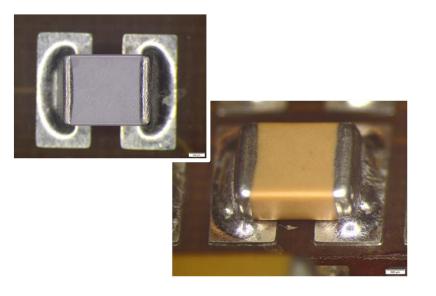

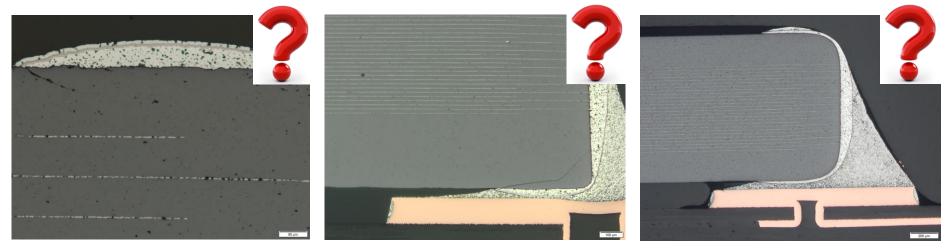

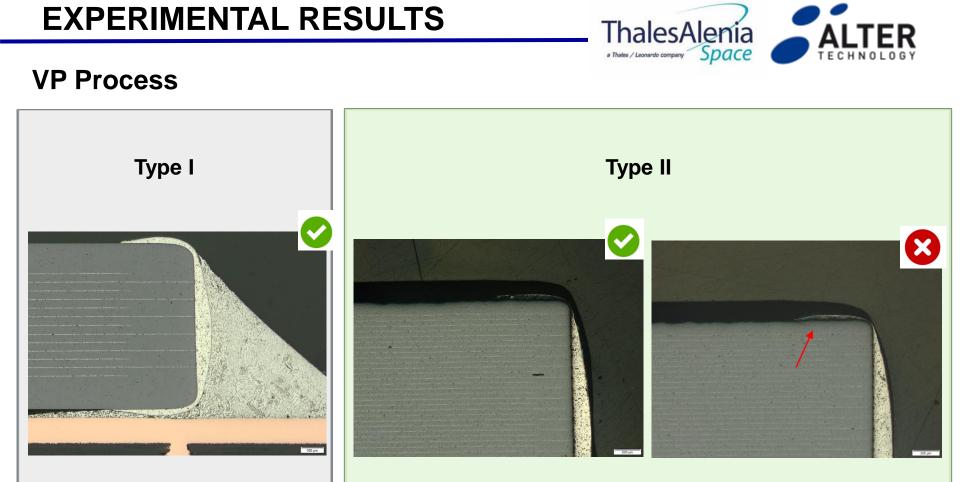

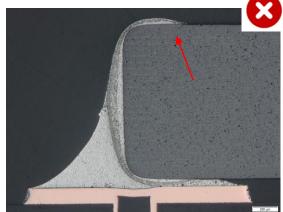

- Type I: No cracks.

- Type II: Some capacitors present cracks in the upper corner.

**VP Process**

Previous test results: Type I: MFR 1, 3 & 4 ok Type II: MFR 2 & 3 ok

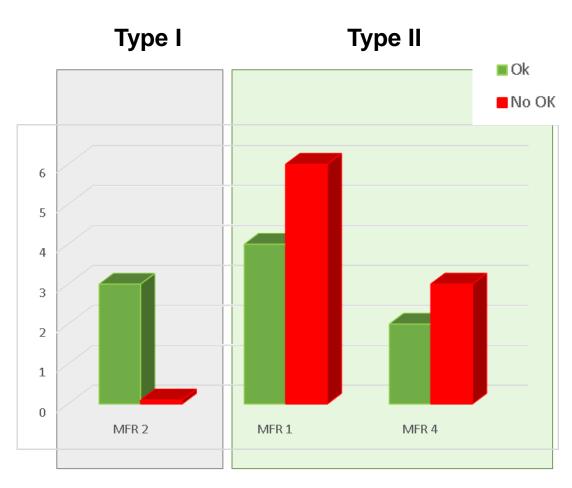

#### Type I: OK Type II: Results are linked to manufacturer.

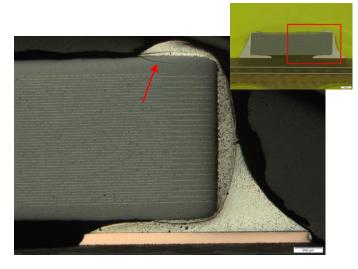

- **MFR 1**: 6 out of 10 capacitors with micro cracks on the top of the component

- MFR 4 (with polymer protection layer): 3 out of 5 with micro crack on the top

**VP Process**

Previous test results: Type I: MFR 1, 3 & 4 ok Type II: MFR 2 & 3 ok

#### Type I: OK Type II: Results are linked to manufacturer.

- MFR 1: 6 out of 10 capacitors with micro cracks on the top of the component

- MFR 4 (with polymer protection layer): 3 out of 5 with micro crack on the top

- No significant differences between ramp 1 and ramp 2.

# **HS Process I**

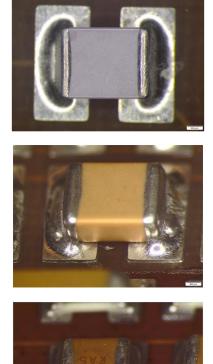

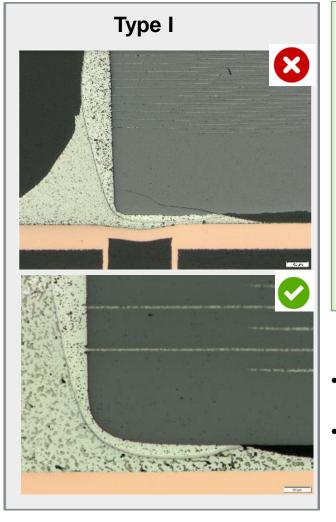

- **Type I**: Some capacitors present cracks.

- Type II: Some capacitors present cracks.

# HS Process I Type I

# Type I: results are linked to manufacturer.

- MFR 2: OK.

- **MFR 3**: 2 out of 3 capacitors with crack in the ceramic.

- **MFR 1**: 3 out of 3 with crack in the ceramic.

- No significant differences between ramp 1 and ramp 2.

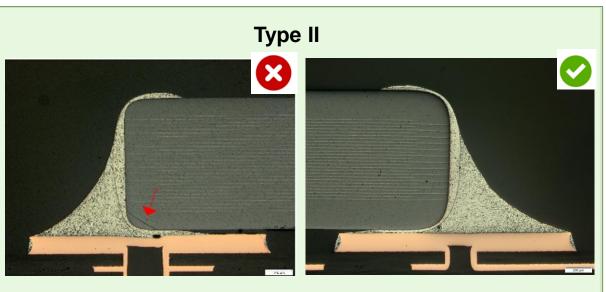

# HS Process I Type II

Type II: results are linked to manufacturer.

#### No satisfactory results

- **MFR 2**: 1 out of 5 with crack in the ceramic.

- **MFR 3**: 2 out of 5 with crack in the ceramic.

- MFR 1: 5 out 5 failed.

- No differences between ramp 1 and ramp 2.

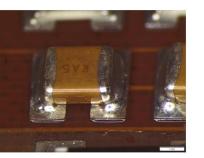

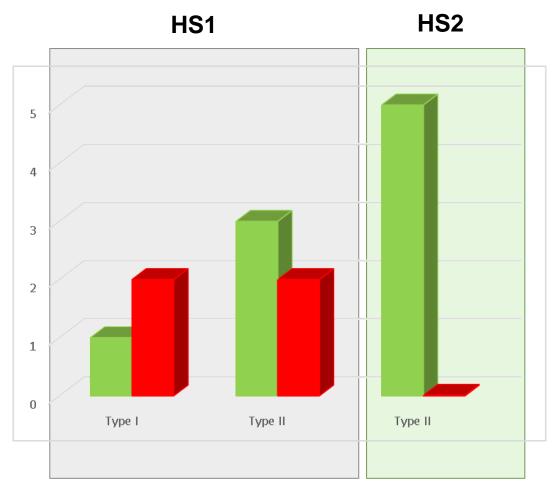

## **HS Process II MFR 3**

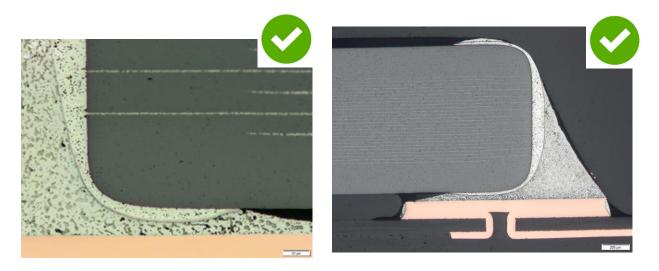

# Hand Soldering process II: satisfactory results

Comparison between type I and type II HS1 and HS2 for the same manufacturer **MFR3**

# CONCLUSIONS

#### VP configuration:

Type I OK Type II Results are linked to manufacturer. Micro cracks on the top in some manufacturers. Others OK.

#### HS1 configuration:

**Type I** and **Type II** Results are linked to manufacturer. Cracks in ceramic bigger than in VP.

#### HS2 configuration:

The results for Hand soldering process II have been satisfactory.

# THANK YOU!

Mari Carmen López Senior Material Specialist mc.lopez@altertechnology.com

+34 954 467 050

TÜV NORD GROUP